University of Southern Queensland Faculty of Engineering & Surveying

### Embedded IP for Small Devices

A dissertation submitted by

Simon Neil Brown

in fulfilment of the requirements of

#### ENG4112 Research Project

towards the degree of

#### Bachelor of Engineering (Computer and Electronic)

Submitted: October, 2005

### Abstract

Today technology utilising the Web is one of the most popular used computer technologies. It would be hard to imagine any computer user whom does not have a web browser or used a web browser. A web browser can view web-pages developed or located within any operating systems, whether that is a Windows, Linux or even iMac workstation. The beauty of this technology is that the web client software (Web Browser) can communicate with any web-server using the Hyper-text Transfer Protocol (HTTP). Also the pages displayed by these systems look identical even though they are generated by a variety of computer systems.

With embedded systems in mind, it would be silly not to utilise this technology for control and monitoring purposes. However, currently small embedded devices, those that are classified with less than 10 kB of ROM, have limited IP connectivity. This is because the current implementations occupy more than the device possesses.

The driver for this research project is the apparent lack of available IP implementations for small embedded devices. Typical embedded IP stacks range from 14kB up to and exceeding 500kB. For small devices, less than 10 kB, this puts this function out of reach.

However, this project aims to implement a subset of Internet Protocols to provide a means of control and monitoring for a small embedded device. It is envisaged that control and monitoring will be achieved with the use of a Web Browser, such as Microsoft "Internet Explorer". The project goals is to provide these services within a 2kB envelope.

University of Southern Queensland Faculty of Engineering and Surveying

#### ENG4111/2 Research Project

#### Limitations of Use

The Council of the University of Southern Queensland, its Faculty of Engineering and Surveying, and the staff of the University of Southern Queensland, do not accept any responsibility for the truth, accuracy or completeness of material contained within or associated with this dissertation.

Persons using all or any part of this material do so at their own risk, and not at the risk of the Council of the University of Southern Queensland, its Faculty of Engineering and Surveying or the staff of the University of Southern Queensland.

This dissertation reports an educational exercise and has no purpose or validity beyond this exercise. The sole purpose of the course pair entitled "Research Project" is to contribute to the overall education within the student's chosen degree program. This document, the associated hardware, software, drawings, and other material set out in the associated appendices should not be used for any other purpose: if they are so used, it is entirely at the risk of the user.

Prof G Baker

Dean Faculty of Engineering and Surveying

## **Certification of Dissertation**

I certify that the ideas, designs and experimental work, results, analyses and conclusions set out in this dissertation are entirely my own effort, except where otherwise indicated and acknowledged.

I further certify that the work is original and has not been previously submitted for assessment in any other course or institution, except where specifically stated.

SIMON NEIL BROWN

0050029170

Signature

Date

## Acknowledgments

To Natalie, Jacqueline and Samuel for their understanding and support during this worthwhile journey.

A special thanks to my supervisor Dr John Leis, who has provided guidance, a source of motivation and friendship over the past year.

SIMON NEIL BROWN

University of Southern Queensland October 2005

# Contents

| Abstract                             | i  |

|--------------------------------------|----|

| Acknowledgments                      | iv |

| List of Figures                      | ix |

| List of Tables                       | xi |

| Nomenclature x                       | ii |

| Chapter 1 Introduction               | 1  |

| 1.1 Overview of the Dissertation     | 2  |

| Chapter 2 Existing System Evaluation | 4  |

| 2.1 Chapter Introduction             | 4  |

| 2.2 Background Information           | 4  |

| 2.3 Short-listed Implementations     | 6  |

| 2.4 Code Size                        | 8  |

| CONTENTS | 5 |

|----------|---|

|----------|---|

| CONT  | TENTS                                        | vi |

|-------|----------------------------------------------|----|

| 2.5   | Functions                                    | 10 |

| 2.6   | Security                                     | 11 |

| 2.7   | Chapter Summary                              | 11 |

| Chapt | er 3 Embedded Platform and Development Tools | 13 |

| 3.1   | Chapter Introduction                         | 13 |

| 3.2   | Microprocessor Core                          | 13 |

| 3.3   | Software and Tools                           | 14 |

| 3.4   | Chosen System: Hardware                      | 15 |

| 3.5   | Chosen System: Software                      | 17 |

| 3.6   | Chapter Summary                              | 20 |

| Chapt | er 4 Software Development                    | 21 |

| 4.1   | Chapter Introduction                         | 21 |

| 4.2   | Software Overview                            | 21 |

| 4.3   | High-level Data Link Control                 | 24 |

| 4.4   | Point to Point Protocol                      | 25 |

|       | 4.4.1 Link Control Program                   | 26 |

|       | 4.4.2 Password Authentication Protocol       | 27 |

|       | 4.4.3 Network Control Protocol               | 28 |

| 4.5   | Internet Protocol                            | 29 |

#### CONTENTS

|        |                                   | •  |

|--------|-----------------------------------|----|

| 4.6    | Transmission Control Protocol     | 30 |

| 4.7    | Hyper-text Transfer Protocol      | 32 |

| 4.8    | RAM Utilisation                   | 33 |

| 4.9    | Code Optimisation                 | 34 |

| 4.10   | Chapter Summary                   | 34 |

| Chapte | er 5 Testing and Security         | 35 |

| 5.1    | Chapter Introduction              | 35 |

| 5.2    | Testing So Far                    | 35 |

| 5.3    | Security                          | 37 |

| 5.4    | Environmental and Hardware        | 38 |

| 5.5    | Chapter Summary                   | 38 |

| Chapte | er 6 Conclusions and Further Work | 39 |

| 6.1    | Achievement of Project Objectives | 39 |

| 6.2    | Further Work                      | 40 |

| 6.3    | Conclusion                        | 42 |

| Refere | nces                              | 43 |

| Appen  | dix A Project Specification       | 48 |

| Appen  | dix B Code Listing                | 50 |

vii

| CONT  | TENTS                                                              | viii |

|-------|--------------------------------------------------------------------|------|

| B.1   | Source Code Listing                                                | 51   |

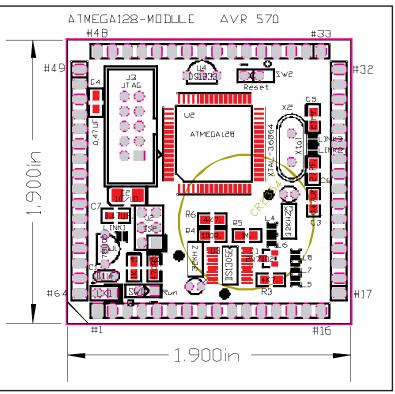

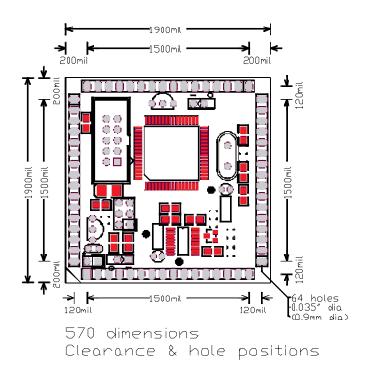

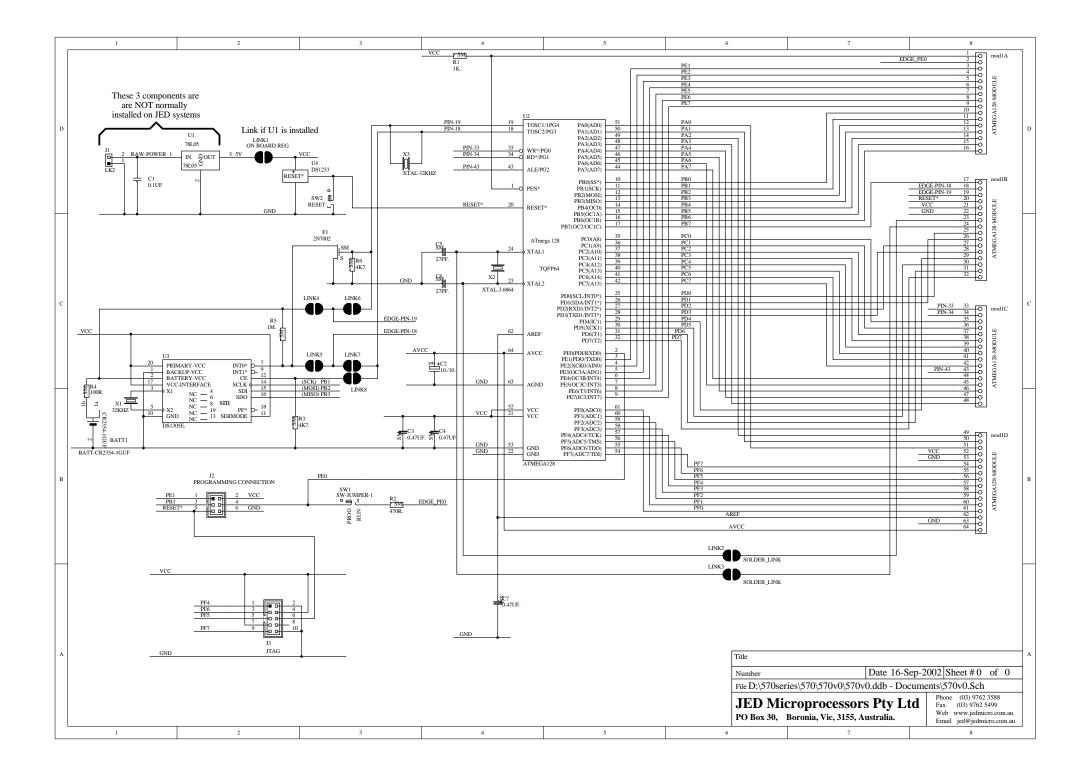

| Appen | dix C Manufacturer Datasheets                                      | 86   |

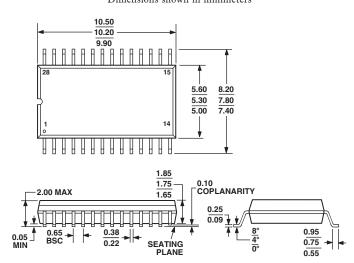

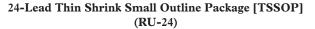

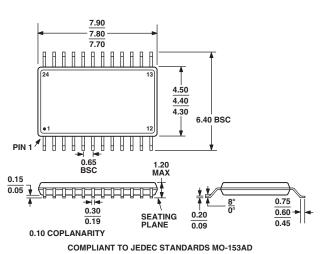

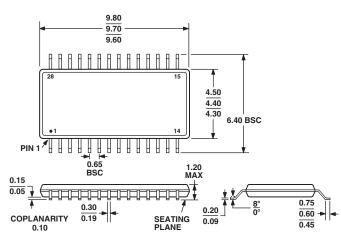

| C.1   | JED Micoprocessor Datasheets                                       | 86   |

| C.2   | AVR ATmega128 Datasheet                                            | 97   |

| C.3   | AVR ISP, In-System Programmer                                      | 125  |

| C.4   | AVR033: Getting Started with the CodeVisionAVR C Compiler $\ldots$ | 128  |

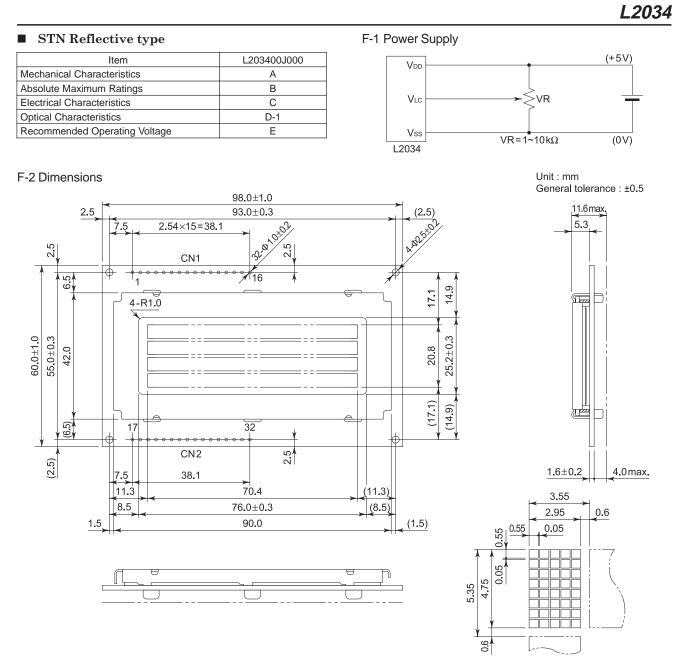

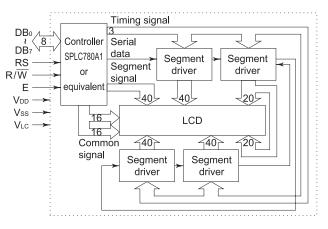

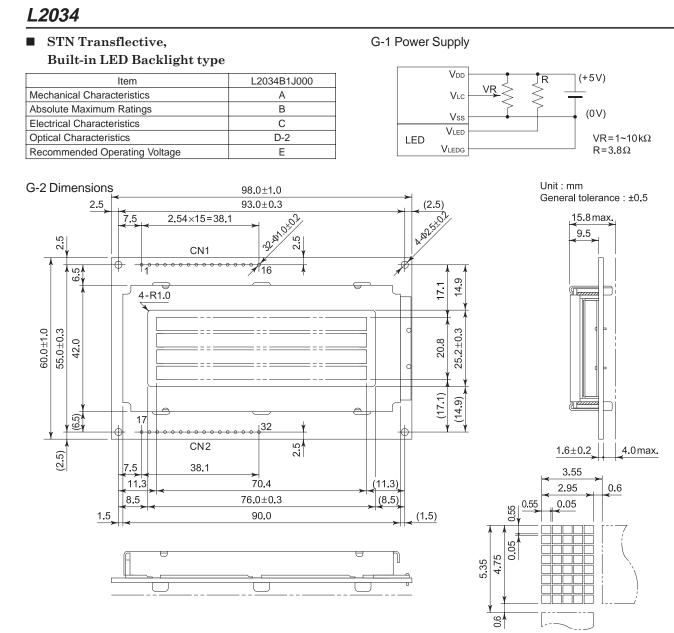

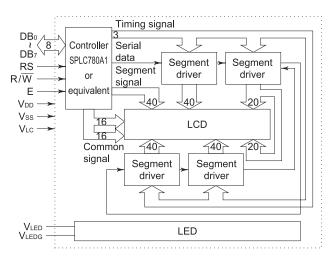

| C.5   | LCD Display Datasheet                                              | 145  |

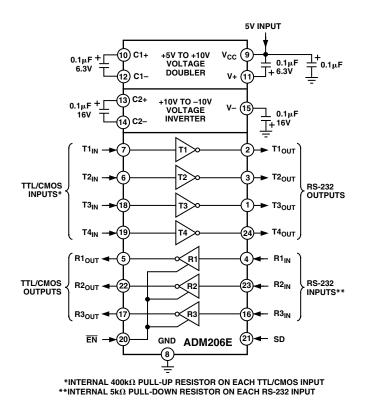

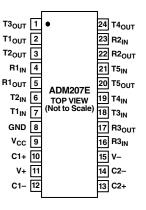

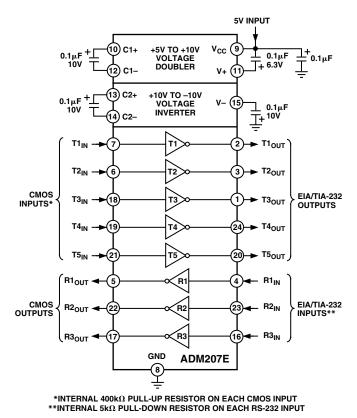

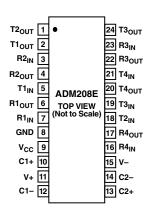

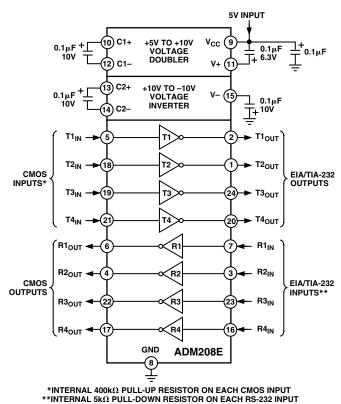

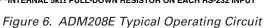

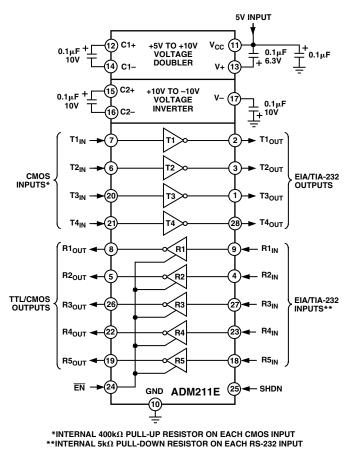

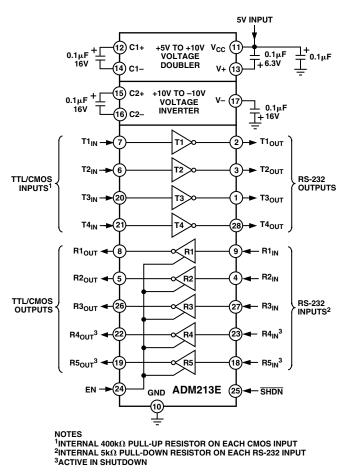

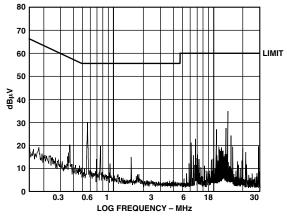

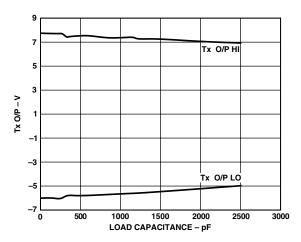

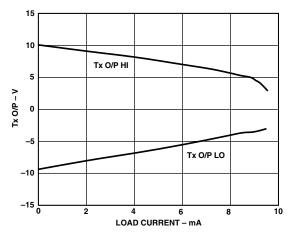

| C.6   | RS232 Transceiver Datasheet                                        | 150  |

# List of Figures

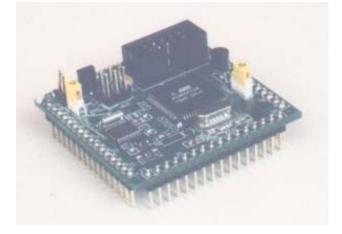

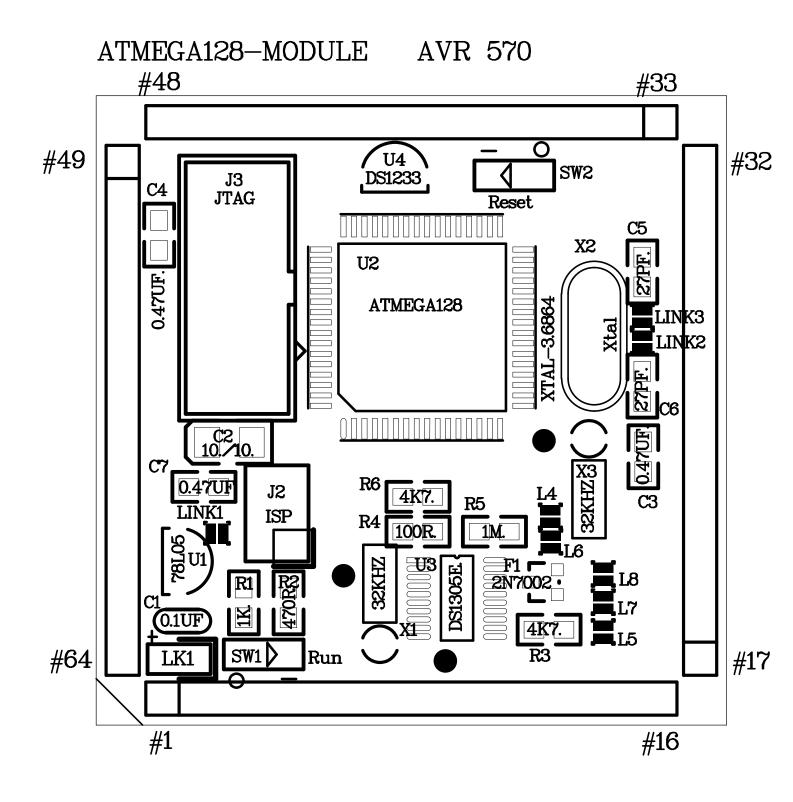

| 3.1 | The AVR570 module from "JED Microprocessor". Note the In-System                                       |    |

|-----|-------------------------------------------------------------------------------------------------------|----|

|     | Programmer interface (top right), reset switch in yellow (bottom left)                                |    |

|     | and the 64 pin surface mounted microcontroller (centre)                                               | 16 |

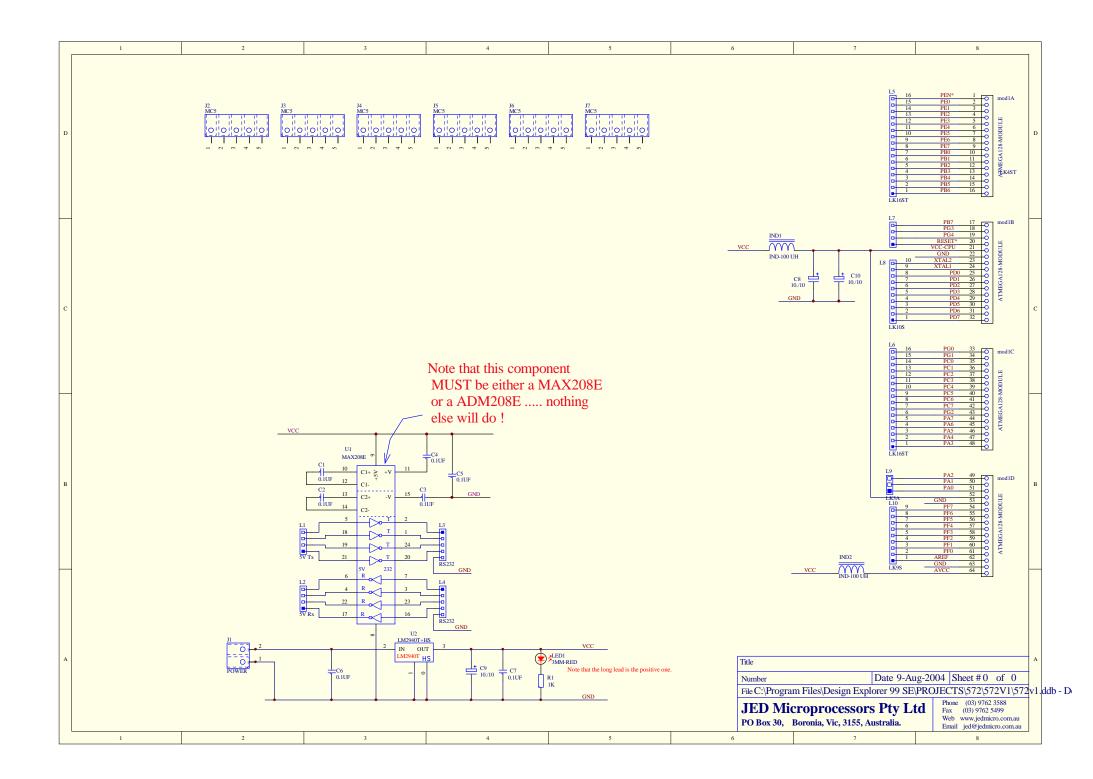

| 3.2 | The AVR572 development board from "JED Microprocessor" revealing                                      |    |

|     | the AVR570 module and the RS232 transceiver and DB-9 connector                                        |    |

|     | (middle left)                                                                                         | 17 |

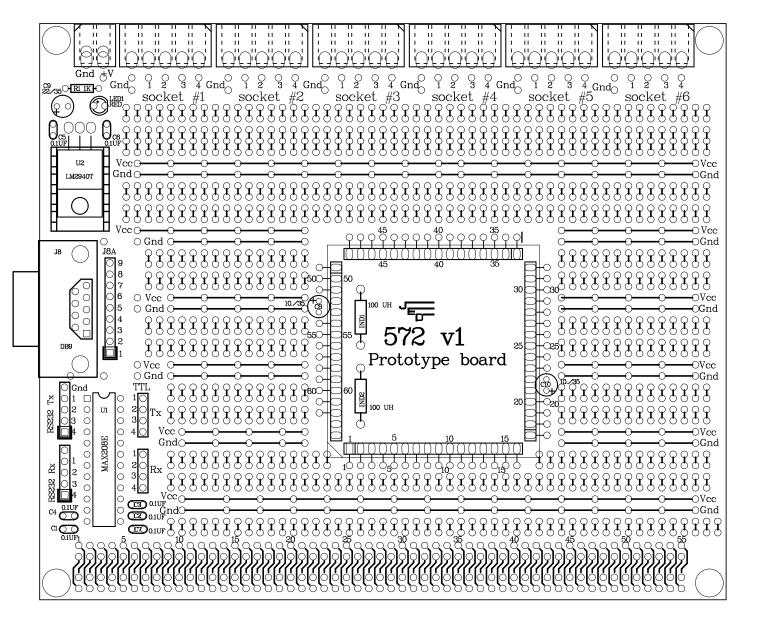

| 3.3 | A screen snapshot of the 'AVRCodeVision' IDE. File management fa-                                     |    |

|     | cilities are revealed on the (left) sub-window with the main coding area                              |    |

|     | (right). Convenient buttons are available for various functions includ-                               |    |

|     | ing, saving, compiling, searching and target programming are located                                  |    |

|     | beneath the pull-down menus. A status message window is available for                                 |    |

|     | debugging and monitoring purposes (bottom) $\ldots \ldots \ldots \ldots \ldots$                       | 18 |

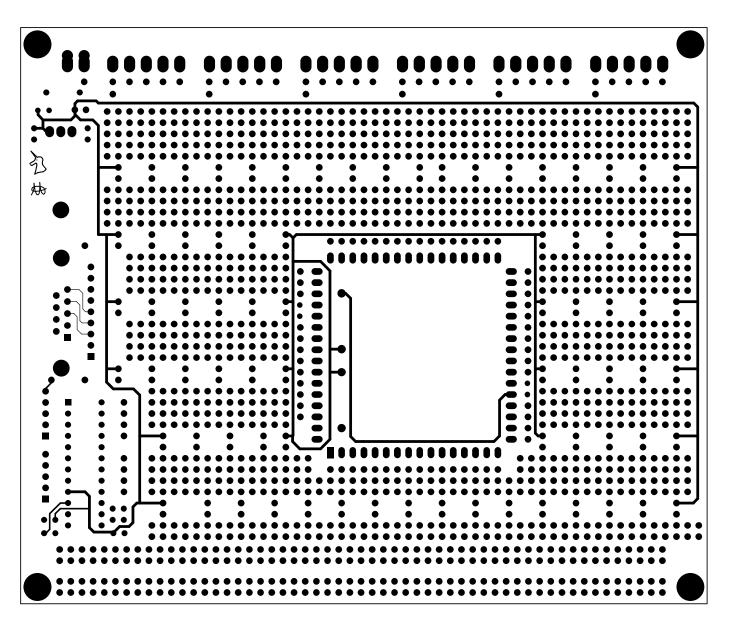

| 3.4 | AVRCodeVision Device Programmer Interface.                                                            | 19 |

| 4.1 | Simplified Flow Diagram.                                                                              | 23 |

| 4.2 | PPP General Frame Format, utilising HDLC                                                              | 24 |

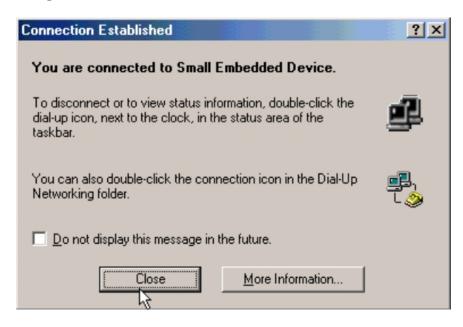

| 4.3 | Windows ME connection established window                                                              | 28 |

| 4.4 | IP Frame, note the relative position of the checksum, which is within                                 |    |

|     | the header. $\ldots$ | 29 |

#### LIST OF FIGURES

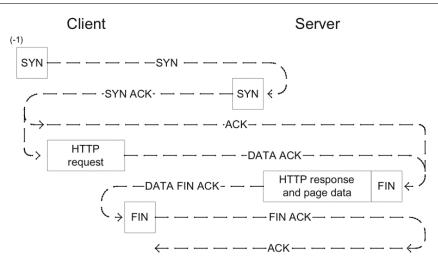

| 4.5 | TCP segment data transfer                                                           | 31 |

|-----|-------------------------------------------------------------------------------------|----|

| 4.6 | Browser Display of Served Web-Page from the embedded device                         | 32 |

| 4.7 | Plethora of packets received on establishment of Link                               | 33 |

| 5.1 | Screen shot of Ethereal Packet Analyser revealing a malformed checksum calculation. | 36 |

$\mathbf{x}$

# List of Tables

| 2.1 | Short-Listed IP Implementations and approximate cost | 7  |

|-----|------------------------------------------------------|----|

| 2.2 | Code Size                                            | 9  |

| 2.3 | Functions for the Short-listed Implementations       | 10 |

| 4.1 | LCP Configuration Options                            | 26 |

# Nomenclature

| PPP   | Point to Point Protocol                            |

|-------|----------------------------------------------------|

| LCP   | Link Control Protocol                              |

| PAP   | Password Authentication Protocol                   |

| IPCP  | Internet Protocol Control Protocol                 |

| IP    | Internet Protocol                                  |

| UDP   | User Datagram Protocol                             |

| TCP   | Transmission Control Protocol                      |

| DHCP  | Dynamic Host Configuration Protocol                |

| HTTP  | HyperText Transfer Protocol                        |

| ASCII | American Standard Code for Information Interchange |

| AT    | Attention                                          |

| CRC   | Cyclic Redundancy Check                            |

| IC    | Integrated Circuit                                 |

| LED   | Light Emitting Diode                               |

| UART  | Universal Asynchronous Receiver / Transmitter      |

| PC    | Personal Computer                                  |

| USQ   | University of Southern Queensland                  |

| CPU   | Central Processing Unit                            |

#### Nomenclature

- ROM Read Only Memory

- IDE Integrated Development Environment

- ISP In-System Programming

- NCP Network Control Protocol

- JVM Java Virtual Machine

- AUD Australian Dollars

- SPI Serial Peripheral Interface

- RTC Real Time Clock

- LCD Liquid Crystal Display

- GPRS General Packet Radio Service

### Chapter 1

### Introduction

Today technology utilising the Web is one of the most popular used computer technologies. It would be hard to imagine any computer user whom does not have a web browser or used a web browser. A web browser can view web-pages developed or located within any operating systems, whether that is a Windows, Linux or even iMac workstation. The beauty of this technology is that the web client software (Web Browser) can communicate with any web-server using the Hyper-text Transfer Protocol (HTTP). Also the pages displayed by these systems look identical even though they are generated by a variety of computer systems.

With embedded systems in mind, it would be silly not to utilise this technology for control and monitoring purposes. However, currently small embedded devices, those that are classified with less than 10 kB of ROM, have limited IP connectivity. This is because the current implementations occupy more than the device possesses.

The driver for this research project is the apparent lack of available IP implementations for small embedded devices. Typical embedded IP stacks range from 14kB up to and exceeding 500kB. For small devices, less than 10 kB, this puts this function out of reach.

However, this project aims to implement a subset of Internet Protocols to provide a means of control and monitoring for a small embedded device. It is envisaged that control and monitoring will be achieved with the use of a Web Browser, such as Microsoft "Internet Explorer". The project goals is to provide these services within a 2kB envelope.

The device will communicate via a PPP link, which would commonly be a serial link (EIA232) interfaced via a modem but just as easily it could just be a direct serial connection to a PC, in the form of EIA232 or USB. The PPP link, together with the IP, will provide the underlying communication path for the higher level protocols such as UDP, TCP and DHCP which in turn provide the baseline software platform to provide the application layer with end to end reliable transport.

The most challenging aspect of this project has been the goal to implement these services utilising only 2kB of text space. Currently the majority of these services have been implemented in 'C' and ported to the end target, with a current code envelope of approximately 8 kB. This dissertation provides a documented journey of this process.

As with all research projects further work is required to engineer the product for manufacture and commercial release and these issues are also briefly discussed.

#### 1.1 Overview of the Dissertation

This dissertation is organized as follows:

- Chapter 2 presents and discusses the evaluation of existing commercial and open source implementations currently available and evaluates them in terms of cost, function and security.

- Chapter 3 discusses, evaluates and selects a suitable micro-controller core, a development environment and a suitable programming language for the development of a working prototype. The evaluation aims to select software tools and hardware to provide a portable system.

- **Chapter 4** discusses the software development with particular attention to the issues faced with small embedded devices with limited resources.

- Chapter 5 discusses testing and security issues and considerations of embedded systems providing IP services.

- Chapter 6 concludes the dissertation and suggests further work in the area of "Embedded IP for Small Devices".

### Chapter 2

### **Existing System Evaluation**

#### 2.1 Chapter Introduction

This chapter presents and discusses the background research and evaluation of existing systems available. Details are revealed of the results of this search and then evaluated in terms of cost, security and function. Commercial and open source products are considered.

#### 2.2 Background Information

In line with the project objectives, as revealed in Appendix A, the first task in the research project programme was the literature research of available systems and the evaluation and review of these systems. For reader ease the first two programme requirements are restated:

- 1. Research available systems.

- 2. Evaluate available systems in terms of cost, security and function, both open source and commercial

#### 2.2 Background Information

Before any review and evaluation studies begun it was important to gain an understanding of the technical requirements and technical nomenclature used in their description. The most concise documentation and literature found was the "Request For Comment" (RFC) documents.

The RFCs provide an open platform for the development of computer networking, focussing on the the "internet". The following RFCs where found to be most useful in the initial understanding of the project technical requirements;

- RFC793: Transmission Control Protocol

- RFC1547: Requirements for an Internet Standard Point to Point Protocol

- RFC1661: The Point to Point Protocol

- RFC2131: Dynamic Host Configuration Protocol

- RFC0791: Internet Protocol

- RFC2616: Hypertext Transfer Protocol

However, it was found that although the RFCs provided a concise specification of the protocols and systems they generally lacked any real world implementation details. Two texts, "TCP/IP Lean" (Bentham 2003) and the ebook "The TCP/IP Guide" (Kozierok 2003-2005) were found to provide more practical and useful information, and were referenced often during the project.

The review process began with an exhaustive search via the internet for commercial and open source implementations. In addition to the "internet" search the resources of the University Library, both USQ and Monash, as well as trade journals (*Embedded Computer Design, Trade Journal* 2005, *PC/104 Embedded Solutions, Trade Journal* 2005)specialising in embedded technology and systems were consulted.

An initial large list of embedded implementations was produced and details pertaining to the products features where recorded on a spreadsheet. Where details were not clearly stated in marketing literature, details were requested, usually by email. In the first iteration 37 products where identified, in various forms, including both commercial and open source products, but was reduced to around 25 in the second iteration.

The list of 25 products was further reduced. In a number of cases insufficient information was available for the evaluation process and consequently these where removed. In most cases it was due to lack of a response to an enquiry. The final list included 17 implementations and is discussed in the next section.

#### 2.3 Short-listed Implementations

It was clear there are abundant commercial and open-source implementations available from the results of my searches. A table of the short-listed implementations was made, primarily filtered to reveal those which supported the services we were interested in, namely PPP, IP, TCP, UDP, DHCP and HTTP.

In an attempt to keep an even playing field, pricing was requested for a single product, complete for a small quantity of product of less than 500 units.

The pricing collected for each product is revealed in Table 2.1<sup>1</sup>. The commercial offerings came with varied and in some cases high price tags. From the literature gathered, the justification for the price tags were summarised as follows:

- a. Fully RFC Compliant

- b. Warranty or Guarantee of stability and function.

- c. Technical Support

- d. Implementations, in some cases, offered for a large range of processors.

- e. Available off the shelf.

- f. Technical Performance such as throughput or memory / resource usage.

<sup>&</sup>lt;sup>1</sup>The majority of quotations were provided in US dollars or Euro and have been converted to Australian dollars. The exchange rate used was 0.77 and 0.597, which was current as of March 2005 for US dollars and Euro respectively.

The pricing did vary between products and it was hard to gauge to what effect the pricing offered reflected product quality, stability, performance or efficiency. Some companies offered demonstration code and differing licensing plans which seemed to indicate different products had differing markets and market focus.

| Product                          | Open Source or | Approximate Price |  |

|----------------------------------|----------------|-------------------|--|

|                                  | Commercial     | (AUD)             |  |

| BLUNK Microsystems               | Commerical     | \$12,730          |  |

| CMX Systems                      | Commercial     | \$12,990          |  |

| EBSnet                           | Commercial     | \$22,100          |  |

| EmINET Microsystems              | Commercial     | \$23,380          |  |

| Ethernut                         | Open Source    | \$0               |  |

| InterNiche Technologies          | Commercial     | \$22,100          |  |

| Iosoft Ltd                       | Commercial     | \$2,300           |  |

| Kadak Products                   | Commercial     | \$27,530          |  |

| MicriUm                          | Commercial     | \$20,150          |  |

| NexGen                           | Commercial     | \$18,700          |  |

| On Time                          | Commercial     | \$11,730          |  |

| Quadros                          | Commercial     | \$20,130          |  |

| Rabbit                           | Commercial     | \$500             |  |

| TINI Network Platform            | Open Source    | \$0               |  |

| Tiny TCP                         | Open Source    | \$0               |  |

| uIP 0.9, Contiki, lwIP & Miniweb | Open Source    | \$0               |  |

| US Software                      | Commercial     | \$25,300          |  |

Table 2.1: Short-Listed IP Implementations and approximate cost

Many of the products listed, are bound by licensing agreements. Licensing agreements are typically offered as single product licences, with and without royalties payable for each product sold, single site licences, for any development at one site or project and unlimited use licences. The unlimited licences usually included technical support for a limited period from purchase.

The Open Source implementations also varied in their nature. Three of the short-

listed implementations didn't include a PPP option, while the fourth, the TINI<sup>2</sup>, has a preloaded 64kB coded section which already contained a network stack. The TINI Dallas product supports full TCP/IP stack, including PPP, and was ready for development in assembly, C or JAVA languages.

#### 2.4 Code Size

In line with the project goals of implementing a stack within a 2kB code envelope, information was gathered relating to the compiled size of a number of implementations. The results are shown in Table 2.2. From the results it was quite interesting to see a large variation in the compiled sizes, even within the same product. However it would be dangerous to make a judgement of these implementations without a detailed evaluation<sup>3</sup>. Nevertheless it is clear from the comparison between the two 'CMX' compilations that the selection of the end target can be important. The selection of differing word platform sizes reveals the efficiency of the compiler math routines, in the case of the two 'CMX' implementations, between 8 bit and 16 bit cores. Mathematics used within the IP and TCP protocols headers use identification and sequencing numbers with numbers ranging from 16 bits to 32 bits, which require large math routines for 8 bit devices and hence the large variations in size.

Characteristic effecting the compiled sizes were found to be:

- 1. Platform word size  $(8, 16, 32 \text{ bit } \dots)$ .

- 2. Instruction word size.

- 3. Technical Performance such as throughput and memory / resource usage.

- 4. Functions offered.

- 5. Differences between compilers and optimisers used.

$<sup>^{2}</sup>$ It may be argued that this implementation should actually be label as "commercial", as the stack is within a purchased product.

<sup>&</sup>lt;sup>3</sup>Which of course could take years to complete and is certainly beyond the scope of this research project.

#### 2.4 Code Size

- 6. RFC compliant.

- 7. Stability and security.

| Product          | Platform                 | Functions        | Code Size(kB) |

|------------------|--------------------------|------------------|---------------|

| uIP              | AVR (8-bit)              | IP, ICMP & TCP   | 5.2           |

| CMX-MicroNet     | Freescale HCS12 (16-bit) | Modem, PPP,      | 14.2          |

|                  |                          | IP, UDP, TCP &   |               |

|                  |                          | HTTP server      |               |

| CMX-MicroNet     | Atmel AVR (8-bit)        | Modem, PPP, IP,  | 33            |

|                  |                          | TCP & HTTP       |               |

|                  |                          | server           |               |

| BLUNK Mi-        | 32-bit Processors        | Full protocol    | 32 to $64$    |

| crosystems       |                          | suite, PPP, IP,  |               |

|                  |                          | TCP, UDP,        |               |

|                  |                          | ICMP, FTP,       |               |

|                  |                          | DHCP etc         |               |

| InterNiche Tech- | Philips 2100 (32-bit)    | Modem, PPP, IP,  | 35            |

| nologies         |                          | TCP & HTTP       |               |

| Iosoft, PWEB     | Microchip PIC (8-bit)    | Modem, SLIP, IP, | 5.7           |

|                  |                          | TCP & HTTP       |               |

| Dallas, TINI     | DS80C400 (8-bit) confirm | PPP, IPv4/v6,    | 64            |

|                  |                          | TCP, UDP,        |               |

|                  |                          | IGMP, ICMP,      |               |

|                  |                          | DAD, SMTP,       |               |

|                  |                          | DHCP, FTP,       |               |

|                  |                          | HTTP, & TEL-     |               |

|                  |                          | NET              |               |

| Table | 2.2: | Code | Size |

|-------|------|------|------|

|       |      |      |      |

#### 2.5 Functions

For completeness, the functions of the short-list are compared to the requirements of the project goals. A comparison is revealed in Table 2.3 of the implementations that supported the services required. It was interesting to note, from the previous table, Table 2.2, that the smallest implementation with the services of interest was 14.2 kB on a 16 bit platform and from 32kB for an 8 bit device.

| Product                          | PPP, IP, UDP, TCP, DHCP & HTTP |  |  |

|----------------------------------|--------------------------------|--|--|

| BLUNK Microsystems               | Yes                            |  |  |

| CMX Systems                      | Yes                            |  |  |

| EBSnet                           | Yes                            |  |  |

| EmINET Microsystems              | Yes                            |  |  |

| Ethernut                         | Yes                            |  |  |

| InterNiche Technologies          | Yes                            |  |  |

| Iosoft Ltd                       | No PPP, only SLIP              |  |  |

| Kadak Products                   | Yes                            |  |  |

| MicriUm                          | Yes                            |  |  |

| NexGen                           | No DHCP                        |  |  |

| On Time                          | Yes                            |  |  |

| Quadros                          | Yes                            |  |  |

| Rabbit                           | Yes                            |  |  |

| TINI Network Platform            | Yes                            |  |  |

| Tiny TCP                         | No PPP                         |  |  |

| uIP 0.9, Contiki, lwIP & Miniweb | No PPP, only SLIP              |  |  |

| US Software                      | Yes                            |  |  |

Table 2.3: Functions for the Short-listed Implementations

#### 2.6 Security

An evaluation of security aspects of embedded system revealed that many of the implementations offer a version of IP called IPsec. This protocol provides encryption of IP data and is a mandatory option of the new IP protocol, IPv6. As with any additional feature additional resources are required to handle the additional overhead of these services.

Other security aspects are the authentication systems available. Of particular interest to PPP is that of the Password authentication Protocol (PAP) and the Challenge Handshake Authentication Protocol (CHAP). These protocols provide methods of authentication to which SLIP does not offer. Virtually all implementations offered PAP and CHAP, however there were a few whom only offered PAP.

Of all implementations evaluated the marketing literature did not seem to discuss issues relating malicious attacks, such as Denial of Service attacks. It seems that software companies do not wish to discuss these issues or possibly there is an inherent weakness in embedded systems?

#### 2.7 Chapter Summary

Investigations have found that there wasn't an implementation that satisfied the project requirements for providing PPP, IP, UDP, TCP, DHCP and HTTP services within a 2kB envelope. However it was interesting to note that two of the open-source implementations, although not providing all the services required, were the smallest at around 6 kB. Generally all the commercial offerings boasted RFC compliant implementations and as a result, the compiled size were a few orders of magnitude greater than the project goal of 2kB, typically 15 to 64kB and varied greatly between 8, 16 & 32 bit implementations.

Further, the commercial offerings gave the impression that they focused on differing markets, and as such it was evident that perhaps there is no interest in development of a "micro" TCP-IP stack. Only time will tell if demand results in a product of this nature entering the main-stream market.

### Chapter 3

# Embedded Platform and Development Tools

#### 3.1 Chapter Introduction

This chapter details the background project requirements for a selection and development tools for development of a working prototype. The working prototype was required to be selected and code developed to implement the IP services required, namely PPP, IP, UDP, TCP, DHCP and HTTP. The following selection describes the selection process of the end core and development tools.

#### 3.2 Microprocessor Core

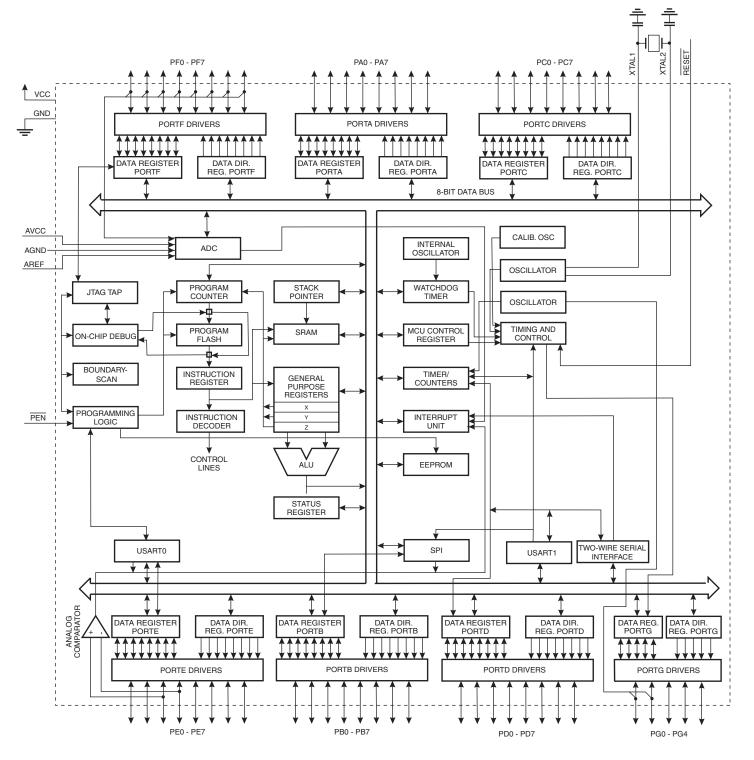

A range of different cores where researched and it was found that a full year of research could be consumed in this process alone. On offer where numerous cores ranging from 8 to 32 bit with a great range of peripherals, including Analogue to Digital Converter (ADC), Timers, comparators, not to mention, flash RAM from kilobytes through to Mega-bytes.

Due to the overwhelming range of cores on offer the evaluation process converged to

a practical process which was further justified by the ever increasing consumption of time. This selection process was therefore judged on what was readily available, had solid tools for support, both for programming and code development, and was well supported by industry.

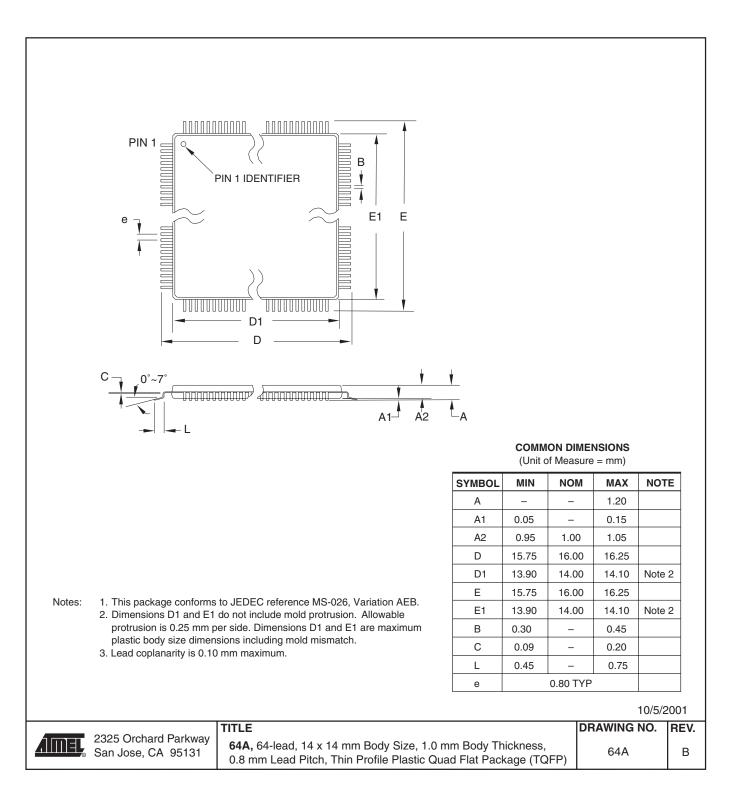

It is clear that the use of a flash RAM device would be beneficial during the development cycle as it could be programmed easily and often. The device therefore would need to have the capability of "In-System Programming" (ISP), where the micro-controller would not be required to be removed from the development circuit to be reprogrammed, further reducing the programming development cycle. Further, with many of the micro-controllers offered only as surface mounted devices, removal from the development board was not practical for reprogramming.

Two manufacturers where short listed based on their availability and wide industry use, the Microchip "PIC" (Peripheral Interface Controller) http://www.microchip. com and ATmels AVR core http://www.atmel.com/products/avr/. Both of these devices boast RISC architecture instruction sets and are 8 bit devices. These devices are available in a wide range of memory configurations and an equally wide range of on-device peripherals.

#### **3.3** Software and Tools

To assist the software development, the use of higher level languages was required as the development of TCP/IP stack would be a challenging task if written in assembly language. Further, the use of assemble language would incur a further learning period to become familiar with the selected platform instructions and its idiosyncrasies. In-line with the project goals is the use of such a language that can provide software portability, as much as practicable in an embedded system. The use of assembly language would therefore diverge from the project goal of providing portability across varying manufactures.

The author has had experience in a number of programming languages during his studies, including Java, Basic, Delphi (Pascal) and 'C'. The 'C' language was chosen

due to its support for virtually all offered IP implementations together with its strong support within the embedded industry and the authors recent exposure within his studies. With these considerations in mind the chosen core would need to have a strong 'C' language compiler support and if possible an integrate development environment in which the core programming and software management functions could be contained as one interface, further reducing the "learning curve".

#### 3.4 Chosen System: Hardware

With the above characteristic in mind the AVR core was selected from the Atmel range of micro-controller devices. Due the large support of these devices, the range of available devices within the AVR range (memory, ADC, Timer etc) and support from numerous compilers, both commercial and open source, this device was an easy choice. Further, from the authors previous experience with the Microchip range of cores, the banked memory architecture has lead to difficulties with programming as the memory is split into banks which do not allow addressing of the complete ROM without setting a bank flag or switch. Microchip have recently improved the architectural design of the memory access problem but backward compatibility may be a problem for this design for portability reasons. The Atmel range, utilising the AVR core, has an identical architecture over devices ranging from 1 to 256 kB of ROM and 64 B to 8 kB of RAM, which allows a wide range from which to choose a hardware platform for the end product target.

As with both manufactures, the devices can be easily programmed in-circuit and the Atmel AVR core boasts more than 10,000 re-write/erasure cycles. This provides a very flexible development system which can easily be ported to a manufacturing environment with relative ease.

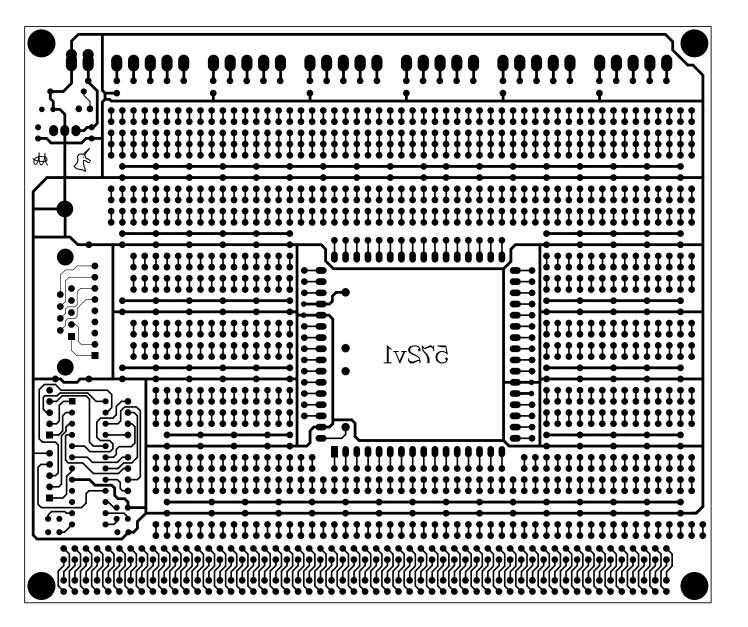

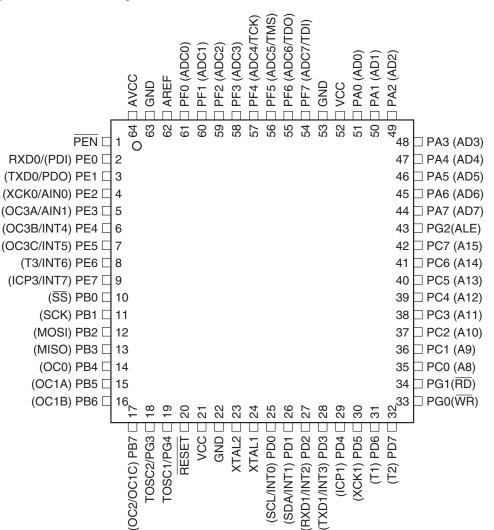

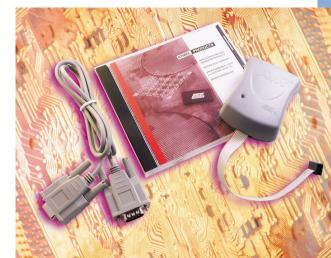

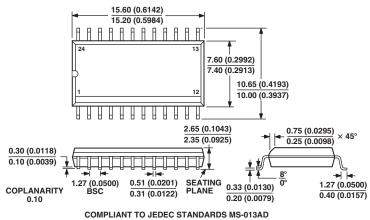

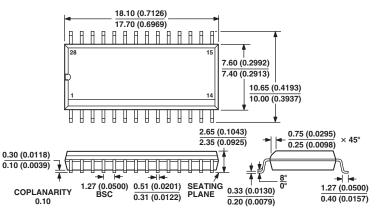

Due to project time constraints a simple development system was procured from "JED Microprocessor Systems" which satisfied the requirements of the previous evaluation requirements. The AVR570 ATmega128 CPU module and AVR572 prototype development board were purchased as well as an ISP (In-System Programmer).

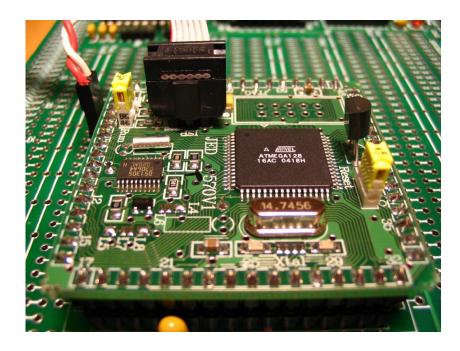

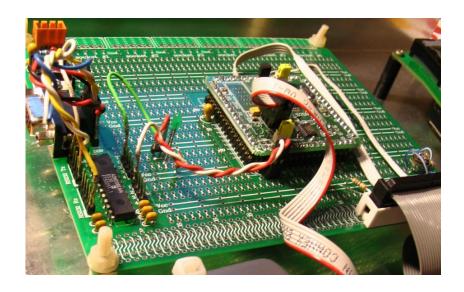

The ATmega128 device boasts 128kB of FLASH ROM and 4kB of RAM, which is more than adequate for this development and was the only device offered in the convenient development platform. This was not considered a problem as the Atmel AVR range of 8 bit devices can easily be scaled onto a device with limited memory and peripherals, if required. The development hardware is revealed in Figure 3.1 and Figure 3.2.

Figure 3.1: The AVR570 module from "JED Microprocessor". Note the In-System Programmer interface (top right), reset switch in yellow (bottom left) and the 64 pin surface mounted microcontroller (centre).

Figure 3.2: The AVR572 development board from "JED Microprocessor" revealing the AVR570 module and the RS232 transceiver and DB-9 connector (middle left)

#### 3.5 Chosen System: Software

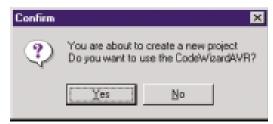

'CodeVisionAVR' by HP InfoTech, http://www.hpinfotech.ro/, was selected because of its wide industry use and strong user support. This compiler supports the 'C' language and provides a user friendly Integrated Development Environment (IDE). The IDE provides project management, including file management, as well as an interface to the Atmel In-System Programmer. Figure 3.3 reveals a screen snapshot of the main interface.

| 🌋 CodeVisionAVR - Embedded IP Stack.prj - [D:\Project\SmallIP\Basic.c]                                                      |

|-----------------------------------------------------------------------------------------------------------------------------|

| Eile Edit Project Iools Settings Windows Help                                                                               |

| ‱ ◘⊱⊟ ⊜ ∽~×≋® ₩₩ ७°°2200% ፨¥% ■ ===∎ ₪ ?                                                                                    |

| Navigator 1109 //***********************************                                                                        |

| CodeVisionAVB 1110 //                                                                                                       |

| Broject Embedde 1111 // HDLC crcCalc                                                                                        |

| 39 Mater                                                                                                                    |

|                                                                                                                             |

| The Other Files                                                                                                             |

| stdlib.h 1115 int i; //Calculate new crc-16 checksum,<br>stdlib.h 1116 unsigned char f; //performed on all bytes after 0x7E |

| lddh 1117 f=checkSumT >8; //performed on all hyces accertativ.                                                              |

| megal28.h 1118 checkSumIn = (checkSumIn & 0xFF) ^ newByte;                                                                  |

| 1119 for (i=0;i=2;i+1){                                                                                                     |

| 1120 if (checkSumIn & 0x01)                                                                                                 |

| 1121 checkSumIn = (checkSumIn >> 1)^ 0x8408;                                                                                |

| 1122 else                                                                                                                   |

| 1123 checkSumIn >>= 1;                                                                                                      |

| 1124 )                                                                                                                      |

| 1125 return checkSumIn^f;                                                                                                   |

| 1126 )                                                                                                                      |

| 1127<br>1128 //***********************************                                                                          |

| 1129 //                                                                                                                     |

| 1130 // addByte                                                                                                             |

| 1131 //                                                                                                                     |

| 1132 //***********************************                                                                                  |

| 1133 unsigned char addByte (unsigned char newByte) {                                                                        |

| 1134 unsigned count =0;                                                                                                     |

| 1135 checkSum=crcCalc(newByte,checkSum); //update CheckSum                                                                  |

| 1136 if (newByte < (unsigned char)0x20) ( //Do we need to insert escape sequence?                                           |

| 1137 txBuff[tx_ptr++]= 0x7D; //insert escape sequence if < 0x20                                                             |

| 1138 txBuff[tx_ptr++]= newByte ^ 0x20; //XOR byte with 0x20 and add.                                                        |

| 1139 count++;                                                                                                               |

|                                                                                                                             |

| Messages                                                                                                                    |

|                                                                                                                             |

|                                                                                                                             |

|                                                                                                                             |

|                                                                                                                             |

|                                                                                                                             |

|                                                                                                                             |

| 1:1 Insert                                                                                                                  |

Figure 3.3: A screen snapshot of the 'AVRCodeVision' IDE. File management facilities are revealed on the (left) sub-window with the main coding area (right). Convenient buttons are available for various functions including, saving, compiling, searching and target programming are located beneath the pull-down menus. A status message window is available for debugging and monitoring purposes (bottom)

AVRCodeVision provides a range of features in which the development of embedded software is enhanced. The IDE provides many features including compiler optimisations, insertion of assembly within the 'C' code, supports the AVR core of the Atmel devices, built in code wizard and code completion tool, as well as supplementary libraries supporting external peripherals such as LCD (Liquid Crystal Displays), RTCs (Real Time Clocks), temperature sensors and various signalling protocols ( $I^2C$ , Dallas 1 wire and SPI). The IDE also supports in-system programming with a simple 1 click compile and program function.

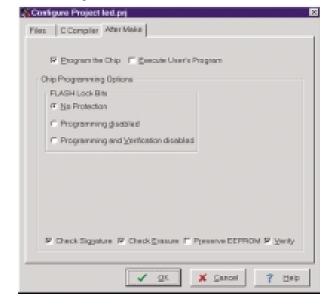

More detailed programming, including the configuration and set-up of the device can also be made via the programmer interface, revealed in Figure 3.4. The "Chip Programmer" provide a means to which the device's contents may be read or written to a file, in addition the set-up of the security configuration can be made to "lock" the device to ensure the contents of the program can not be copied or overwritten.

| CodeVisionAVR Chip I                                                                                                                                                      | Programm                                                      | ier - At                         | mel STK500/AV                                                                                                                                             | risp 🛛 🔀   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| File Edit Program Read                                                                                                                                                    | Compare H                                                     | Help                             |                                                                                                                                                           |            |

| Chip: <mark>ATmega128 ▼</mark><br>FLASH<br>Start: 0 h End: 1<br>Checksum: 7F44h                                                                                           | 093 h                                                         | EEPR<br>Start:                   | IOM                                                                                                                                                       | Beget Chip |

| Chip Programming Options<br>FLASH Lock Bits<br>No Protection<br>Programming disable<br>Programming and V<br>Boot Lock Bit 0<br>B01=1 B02=1<br>B01=0 B02=0<br>Dot 10 B02=0 | ed<br>erification dis<br>Boot Lock<br>B11=1<br>B11=0<br>B11=0 | Bit 1<br>B12=1<br>B12=1<br>B12=0 | Fuse Bit(s):<br>CKSEL0=0<br>CKSEL1=0<br>CKSEL2=0<br>CKSEL3=0<br>SUT0=0<br>SUT1=0<br>BODEN=0<br>BODEVEL=0<br>BOOTSZ1=0<br>BOOTSZ1=0<br>CKOPT=0<br>JTAGEN=0 |            |

| © B01=1 B02=0                                                                                                                                                             | C B11=1                                                       | 812=0                            | CCDEN=0                                                                                                                                                   | <b>~</b>   |

| Check Signature                                                                                                                                                           | Check <u>E</u> ras                                            | ure 🗌 f                          | Preserve EEPROM                                                                                                                                           | ✓ Verify   |

Figure 3.4: AVRCodeVision Device Programmer Interface.

#### 3.6 Chapter Summary

This chapter has evaluated a range of hardware platforms and software development tools. This evaluation phase has established a baseline from which the development of a working prototype can be made. The process has successfully evaluated and selected an end core, namely the Atmel AVR, to which a portable software implementation can be made. The use of the AVRCodeVision IDE will provide the necessary software and hardware tools to foster the software development. The use of 'C' as a programming language will provide the portability due to its strong industry support, not only within the Atmel AVR range but also across a large range of end hardware platforms.

### Chapter 4

### Software Development

#### 4.1 Chapter Introduction

In this chapter I will describe the software implementation of the Internet Protocols with an aim to provide the services within a 2kB envelope. This is certainly a challenging task to squeeze this into a small code size. It was discovered early in the project that to meet this objective certain compromises would need to be made to minimise the code and as such is main technical challenge of this Research Project.

The Internet Protocols implemented, namely PPP, IP, TCP and HTTP, will be described. Firstly an overview of the generic framework will be presented from which the IP software is built upon. The TCP/IP protocols required to serve a simple web-page will be discussed, beginning with the Host to Network layer (RS232 & PPP) through to the Application layer (HTTP).

#### 4.2 Software Overview

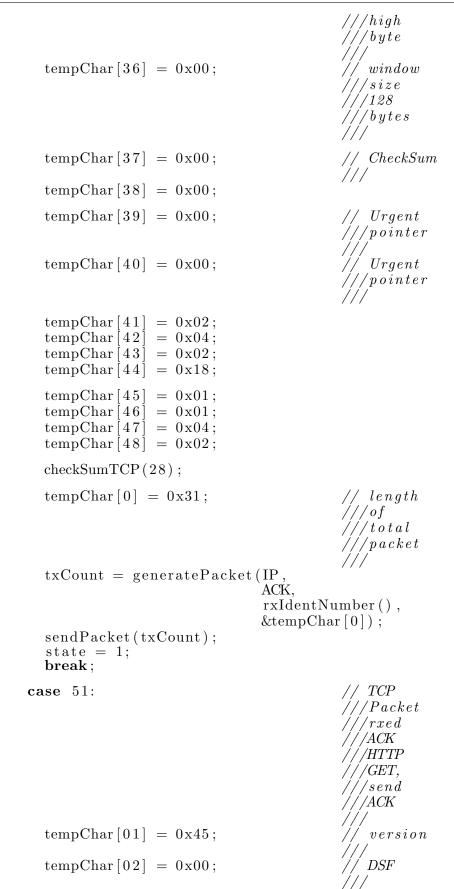

The underlying software structure provides device initialisation, modem emulation, packet reception, packet transmission and link termination. The system was developed with Windows 98 PPP client, a terminal application Comlab (Vanstan 2003) and a

#### 4.2 Software Overview

popular packet analyser Ethereal (Combs 2005).

After reset the device is initialised. The initialisation routine configures the ports and importantly the communication port to which the device communicates. The software then provides responses to modem commands issued by the PC as the device is directly connected to the PCs serial port. When the fundamental data link has been established the software waits for a data stream.

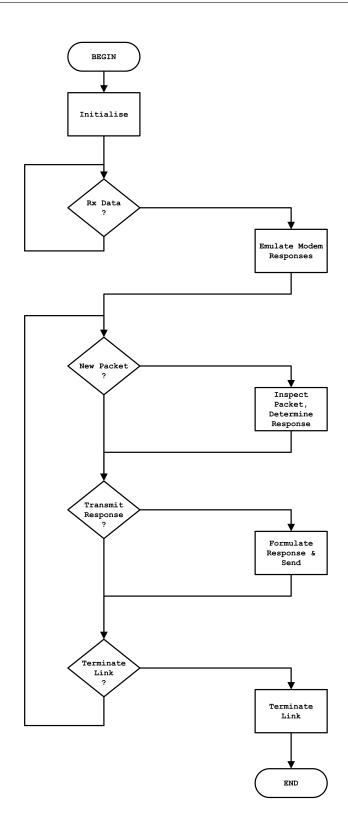

When a data stream is received and stored it is inspected. The inspection process determines what course of action it should take. If the packet is unrecognised or one of which it is not interested in it is silently discarded. If a response is required a packet is generated and sent via the communication port. A simplified flow diagram of the software structure is revealed in Figure 4.1.

Figure 4.1: Simplified Flow Diagram.

A number of supporting functions are called during this process. They include reception and transmission routines, various checksum calculations, insertion of escape sequences and packet inspection functions.

#### 4.3 High-level Data Link Control

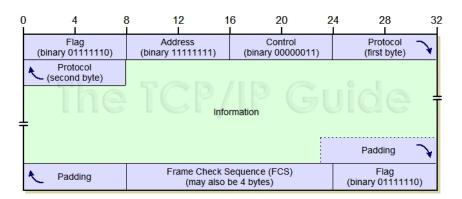

The basis for all communication within the Point to Point Protocol is via the HDLC data link control protocol. In this implementation the HDLC is used to encapsulate the higher level protocols over an EIA232 link. In this case the HDLC protocol operates over an asynchronous link and includes error detection via a Frame Check Sequence. Figure 4.2 reveals the HDLC frame (Kozierok 2003-2005).

Figure 4.2: PPP General Frame Format, utilising HDLC.

With PPP the first three bytes are fixed in value. They are the Flag, Address and Control fields, and are fixed as the link only ever connects between two hosts. It is important to note that PPP doesn't conform to HDLC rules, it uses HDLC as the basis for its structure. The next field (protocol) specifies the protocol of the information payload. In this implementation the protocol fields of interest are LCP, PAP, IPCP, and IP. The higher level protocols, TCP and HTTP, are contained within the IP information payload.

The start and end of each packet is signified with 7E hexadecimal (01111110 Binary) and provides a means to detect the packet. As mentioned previously the HDLC packet utilises error detection using a FCS. This is calculated over the entire frame, excluding

the start and ending Flags, and is positioned at the end of the frame. The position of the FCS is convenient as it is calculated as the packet is being transmitted. The calculation of IP and TCP checksum is a little more tricky as the checksums are positioned within the headers, and as such the the checksums are required to be calculated prior to passing them to the lower level protocols for subsequent transmission.

The PPP packet is then transmitted with the start Flag, Address, Control, protocol field, information payload, FCS and end Flag. However any byte within the frame that is less than 20 hexadecimal or is 7E or 7D hexadecimal is treated differently. If such a byte is found within the stream the byte is first exclusive-ORed with 20 hexadecimal and transmitted with a 7D hexadecimal followed by the exclusive-ORed byte.

In this implementation the PPP frame is generated in a buffer, the FCS calculated and then the buffer is sent to a transmission routine where the bytes are scanned to see if they match the above criteria (< 20, 7E or 7D Hexadecimal) and sent.

#### 4.4 Point to Point Protocol

PPP is a protocol that enables links over a variety of different physical layer connections. In this implementation it is being utilised over EIA232, formally known as RS232, however it can also operate over other mediums, such as USB and ethernet. It can carry any type of network layer datagram, however we are only interested in the IP and UDP protocols in this implementation.

PPP has taken over from the Serial Line Internet Protocol (SLIP) mainly due to the former having security features such as authentication, the ability to support other protocols other than IP and ability to dynamically allocation IP addresses during the link establishment phase.

As we have briefly discussed in the preceding section, PPP operates using a HDLC-like data link control protocol and provides a means to which two hosts can communicate with Internet Protocols. However, before we can authenticate the user and exchange data over the link, we must configure it. This is achieved within this implementation via the Link Control Protocol, the Password Authentication Protocol and the Network Control Protocol.

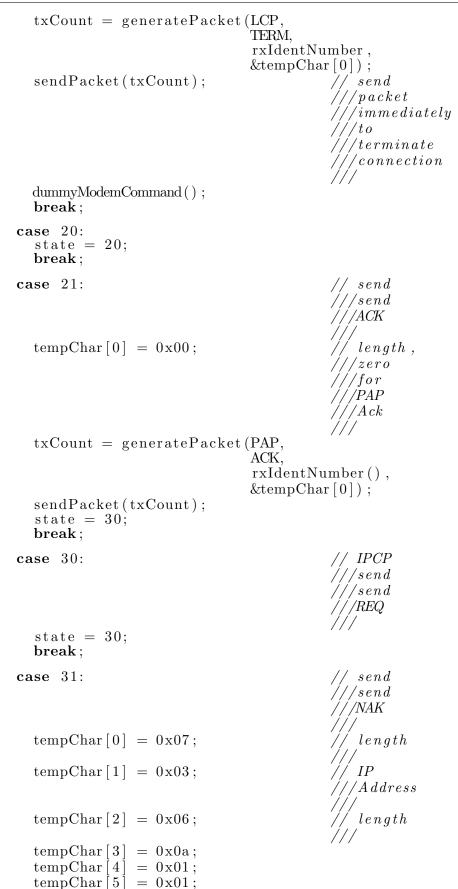

#### 4.4.1 Link Control Program

This protocol is used to establish, configure and test the data-link. Firstly the PPP link sends LCP packets to configure and test the data link. After each side of the link has agreed to its peers configuration the basic link is established.

The protocol uses a system of requests, acknowledgements, negative-acknowledgements to negotiate the options. However there are also may other configuration controls, reference should be made to RFC1661 (Simpson 1994b) for full implementation details. This implementation provides the minimum negotiations required to establish the protocol and is far from RFC compliance. This wholly justified by the fact that the project goal is to provide a very small IP implementation. The implementation of an RFC compliant design would therefore consume a large envelope of code diverging from the project goal.

There are a number of configuration items that can be negotiated. In this implementation configuration of the minimum number of options to establish a link was made. The minimum options for the peer are 2, 5, 7 and 8, whereas for the host (embedded device) options 3,5, 7 and 8 were required. The options of interest are revealed in the Table 4.1. It was found that the link could not be established, with the Windows 98 client, with any less than the options listed. Any attempt to reduce the options resulted in the peer not agreeing and hence terminating the link.

| Option | Descritption                           |

|--------|----------------------------------------|

| 2      | Maximum Receive Unit                   |

| 3      | Authentication-Protocol.               |

| 5      | Magic Number                           |

| 7      | Protocol-Field-Compression             |

| 8      | Address-and-Control-Field-Compression. |

Table 4.1: LCP Configuration Options

The LCP configuration option 2 signifies that the host can receive larger packets, or to request that the peer send smaller packets.

The default value is 1500 octets which seems to indicate it matches the maximum size of an ethernet frame. However it was noticed during development that even if this option was reduced, to say 200 bytes, the peer ignored the request and continued to sent larger packets. Inspection of RFC1661 revealed the following "If smaller packets are requested, an implementation MUST still be able to receive the full 1500 octet information field in case link synchronisation is lost.", however it didn't seem to have any bearing if synchronisation was not lost.

Option 3 of the LCP configuration specifies the authentication protocol. This may be either the Password Authentication Protocol (PAP) or Challenge Handshake Authentication Protocol (CHAP). The PAP authentication type was selected and negotiated as it was simple to implement, whereas the CHAP requires a considerable overhead in terms of software relative to PAP. PAP simply provides a mechanism to which a UserID and Password are sent, in plain text, from the peer requesting the authentication. The host then authenticates the requester by sending an acknowledgement. Conversely if the UserID or Password are incorrect the host sends a Rejection.

The last two options 7 and 8 provide a means to which information within the HDLC frame may be omitted to improve the through-put of the link. The first three bytes of the HDLC frame, after the initiating Flag (7E), are always fixed. When this compression is in use these bytes are simply not transmitted. However, each peer may still transmit these bytes if it so desires. In this implementation these bytes are always transmitted as it reduces the code envelope.

#### 4.4.2 Password Authentication Protocol

Once the initial Link is established the authentication process begins with the negotiated protocol PAP (option 3 in the LCP negotiation). The UserID and Password pair is sent to the authenticator and if authenticated a Acknowledgement is sent.

In this implementation the software looks for a PAP packet with a REQ (Request) from

the peer and acknowledges that request. Currently the software provides no password or user ID checking.

#### 4.4.3 Network Control Protocol

The Network Control Protocol is a used to configure each network protocol which intends on utilising the data link by use of network protocol configurations. For the case of IP, the configuration protocol used is the Internet Protocol Control Protocol (IPCP). With this protocol the IP configuration is negotiated and established. Such things as, DNS, Gateway, netmasks and IP addresses can be configured with this protocol. In this implementation the IP address for both the host and the peer is made. Again, the minimum configuration was negotiated, that being the IP addressing of the host and client only.

After the negotiations have been made and agreed by both hosts the Host to Network layer is established and the link is available to accept IP traffic. In Windows the clients signifies this by popping up a window confirming you have made a connection to your host, as in Figure 4.3.

Figure 4.3: Windows ME connection established window.

#### 4.5 Internet Protocol

At this stage we have successfully negotiated and established a PPP link which carry our IP datagrams, which in turn carry the higher level protocols TCP and HTTP.

The implementation of the IP packet was relatively trouble-free as once the PPP link is established it is just a matter of filling up the transmit buffer for the lower layer to send. The only difficulty was the implementation of the checksum as it is located within the header which is at the front of the datagram. Recall the checksum for the HDLC frame is at the end of the data stream and was easy to calculate as bytes were transmitted. In the IP case this involved the use of another temporary buffer in which the checksum could be calculated prior to passing it to the lower layer.

Figure 4.4 reveals the datagram format detailing the position of the checksum within the datagram.

| ver                 | len            | type     | Total Length    |        |  |  |  |  |

|---------------------|----------------|----------|-----------------|--------|--|--|--|--|

|                     | ide            | ent      | f               | offset |  |  |  |  |

| T                   | ГL             | Protocol | Header Checksum |        |  |  |  |  |

|                     | Source Address |          |                 |        |  |  |  |  |

| Destination Address |                |          |                 |        |  |  |  |  |

| Data                |                |          |                 |        |  |  |  |  |

Figure 4.4: IP Frame, note the relative position of the checksum, which is within the header.

IP provides a means in getting datagrams from the source to their destination. This is achieved with addressing the datagram. As can be seen in Figure 4.4, the IP header contains fields for the IP source and destination addresses. In this implementation they are statically set however, using DHCP these could be dynamicly made.

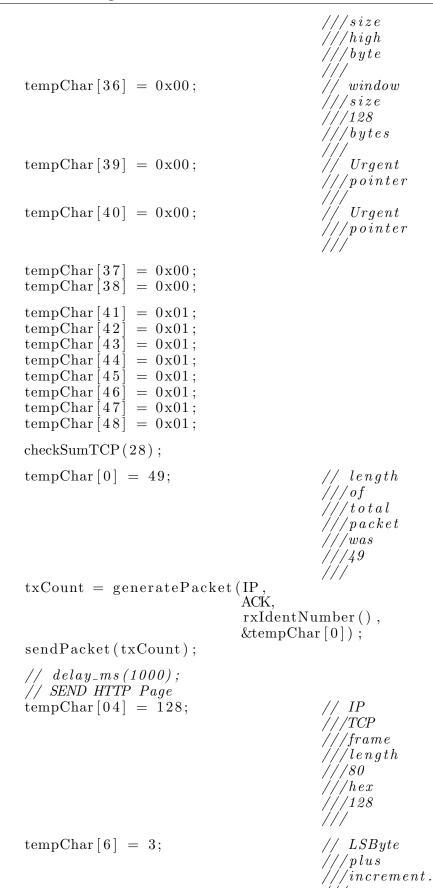

#### 4.6 Transmission Control Protocol

The Transmission Control Protocol (TCP) proved to be the most challenging aspect of the software development. As TCP is a connection orientated protocol it provides mechanisms to ensure that data send over the link reaches its destination. This involves the establishment of a logical connection, the passing of data and an acknowledgement that the data is received. In addition each unique data transfer is handled in this set-up and acknowledge method separately.

TCP first requires a connection to be established and in the case of a client requesting a web-page the client first sends a SYN to begin the process. The server in this case also sends a SYN and an ACK to the acknowledge the SYN. TCP provides a means to which ACKs can be piggybacked to reduce traffic, as in the case of a SYN and ACK in one response. Once this initial handshaking has taken place the client requests a web-page with the HTTP GET command and also piggybacks the ACK to the previous server response. The server then replies with a HTTP response, in this implementation in the form of a HTTP/1.0... "Hello World", with an ACK to the previous segment to signify it has received its request. Again the client sends an ACK to acknowledge the reception of the webpage, and the server sends another ACK to acknowledge the clients ACK. At this stage the web-page can be displayed. The webpage is only displayed when the client knows the transfer has been received in order and that it is all it should receive. Figure 4.5 (Bentham 2003) reveals this process described, note the use of piggy-backing to reduce network traffic.

Figure 4.5: TCP segment data transfer.

In addition to the handshaking taking place TCP provides a mechanism to ensure that the segments transmitted are sequenced. As packets can be received out of order each segment transmits a 32 bit sequence number which identifies the start of each segment. When the peer acknowledges the segment it also acknowledges the sequence number which is incremented by the number of bytes received in the TCP datagram. Subsequent segments transmitted increment the sequence number by the size of payload so that the receiver can determine the order in which the data should be placed in. In this implementation the segment size has been kept small, less than 500 bytes, to reduce the software management if datagrams where split over multiple packets.

TCP implements the sliding window method of data transfer to improve link efficiency which is also another function of the sequence numbering. As the embedded device has limited RAM, the window size has been limited to ensure that it only ever needs to keep track of one segment (one packet). This has the secondary advantage of reducing the software complexity and hence code size.

The second challenge of TCP was the calculation of the checksum. In TCP the checksum is not only is calculated over its header and payload, as a conventional checksum is calculated, but also included is information from the IP layer. This provides additional measures to ensure the TCP segment is directed to its intended recipient. It was interesting to note that this violates the architectural layering principles of the OSI model in which each layer is a self contained unit.

The TCP checksum is calculated with a "Pseudo Header" and included within the Pseudo Header is IP source and destination addresses, the IP protocol field (from the lower IP layer) and the computed TCP length.

This presented some difficulties with the calculation as the TCP and IP layers were closely bound. The software implementation therefore, was closely bound in the way it operated as such we had two checksum to calculate prior to passing this down to the PPP link for transmission.

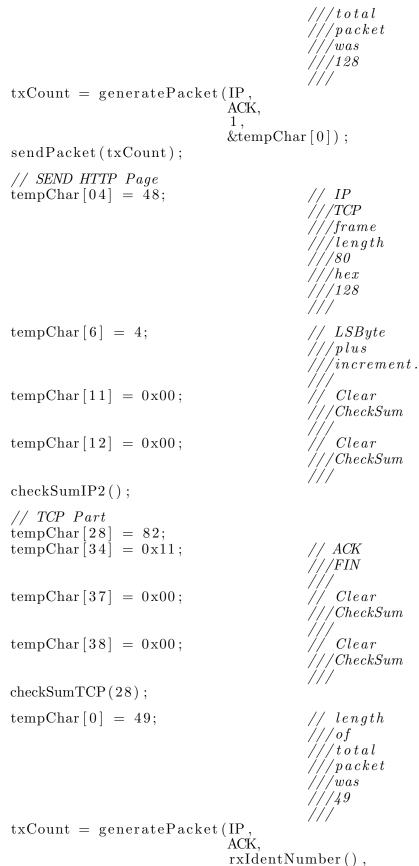

#### 4.7 Hyper-text Transfer Protocol

The application level protocol used to send and receive web-pages is the Hyper-text Transfer Protocol. It provides a simple method of requesting web-pages from servers and the format of the data from the server. In this implementation the device looks for the "GET" ASCII byte sequence within the TCP payload. The device then reply to this request with a simple response, in this case a static web-page is displayed. Figure 4.6 reveals the first web-page served on the embedded device.

| 🎒 http:/              | //10.1.1.2/      | / - Microsol       | it Internet I            | Explorer  |               |                |            |              |                    | ļ                 | - 🗆 × |

|-----------------------|------------------|--------------------|--------------------------|-----------|---------------|----------------|------------|--------------|--------------------|-------------------|-------|

| <u>F</u> ile <u>E</u> | dit <u>V</u> iew | F <u>a</u> vorites | <u>T</u> ools <u>H</u> e | lp        |               |                |            |              |                    |                   |       |

| √⊒<br>Back            | →<br>Forward     | 🚽 🐼<br>Stop        | 🕼<br>Refresh             | 🛱<br>Home | ्रि<br>Search | 🛞<br>Favorites | 💮<br>Media | 🌀<br>History | ⊠ <b>▼</b><br>Mail | <b>S</b><br>Print | »     |

| A <u>d</u> dress      | 🅘 http://1       | 0.1.1.2/           |                          |           |               | • ć            | >Go Lir    | nks ど Be     | st of the W        | /eb               | »     |

| Finally               | r some thir      | JE                 |                          |           |               |                |            |              |                    |                   | A     |

| ど Done                |                  |                    |                          |           |               |                |            |              | 🤣 Interne          | et                | /     |

Figure 4.6: Browser Display of Served Web-Page from the embedded device.

The implementation of this protocol was straightforward and only required the testing of the TCP datagram, for a GET and the simple formulation of a static web-page which was passed down to the TCP layer.

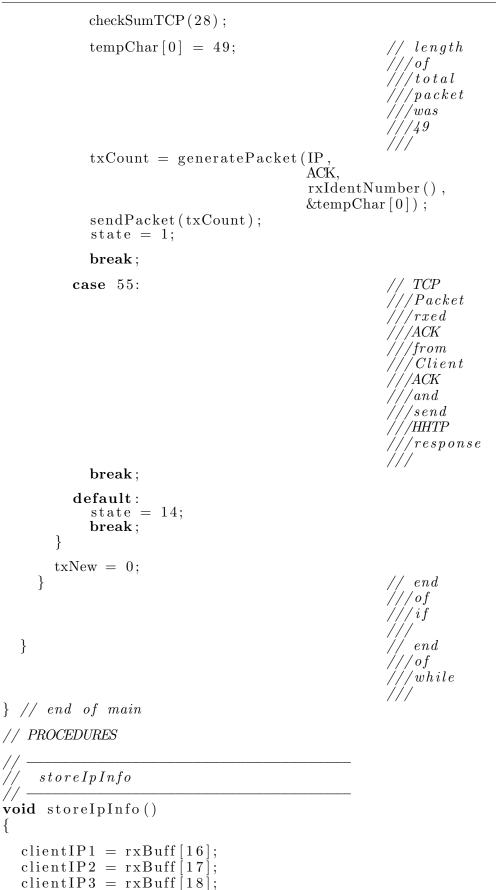

#### 4.8 RAM Utilisation

Currently the software utilises approximately 3kB of RAM. This is made up of 2 buffers of 1kB for transmission and reception, in addition to a temporary buffer of 768 Bytes plus the stack of approximately 240 Bytes. The transmit and temporary can be reduced in size to around 150 Bytes. However the receive buffer needs to be larger as it was found that some packets can cause a buffer over-run. This was caused by the plethora of packets received once the link was established, and also as it is idle, and is revealed in Figure 4.7.

| 🕙 13JulyDump - Eth                        | real                       |                       |                                                                               |     |

|-------------------------------------------|----------------------------|-----------------------|-------------------------------------------------------------------------------|-----|

| <u>File E</u> dit <u>Vi</u> ew <u>G</u> o | Capture Analyze Statistics | Help                  |                                                                               |     |

| en en en en                               | 🛍 i 🗁 😭 🗙                  | r 🖓 📇 🖓               |                                                                               |     |

| Eilter:                                   |                            | •                     | Expression Clear Apply                                                        |     |

| No Time                                   | Source                     | Destination           | Protocol Info                                                                 |     |

| 29 256.152456                             | 10.1.1.1                   | broadcast             | AKP WHO HAS IV.I.I.I GRATUITOUS AKP                                           | - 6 |

| 30 256.975795                             | 10.1.1.1                   | 224.0.0.2             | ICMP Router solicitation                                                      |     |

| 31 258.174745                             | 10.1.1.1                   | 10.255.255.255        | NBNS Registration NB TANGLES <oo></oo>                                        |     |

| 32 258.285568                             | 10.1.1.1                   | 10.255.255.255        | NBNS Registration NB WORKGROUP<00>                                            |     |

| 33 258.390619                             | 10.1.1.1                   | 10.255.255.255        | NBNS Registration NB TANGLES<03>                                              |     |

| 34 258.920469                             | 10.1.1.1                   | 10.255.255.255        | NBNS Registration NB TANGLES<00>                                              |     |

| 35 259.030470                             |                            | 10.255.255.255        | NBNS Registration NB TANGLES<03>                                              |     |

| 36 259.140468                             | 10.1.1.1                   | 10.255.255.255        | NBNS Registration NB WORKGROUP<00>                                            |     |

| 37 259.675352                             |                            | 10.255.255.255        | NBNS Registration NB TANGLES<00>                                              |     |

| 38 259.785327                             |                            | 10.255.255.255        | NBNS Registration NB WORKGROUP<00>                                            |     |

| 39 259.890341                             |                            | 10.255.255.255        | NBNS Registration NB TANGLES<03>                                              |     |

| 40 259.975347                             |                            | 224.0.0.2             | ICMP Router solicitation                                                      |     |

| 41 260.429375                             | 10.1.1.1                   | 10.255.255.255        | NBNS Registration NB TANGLES<03>                                              |     |

| 42 260.540229                             | 10.1.1.1                   | 10.255.255.255        | NBNS Registration NB WORKGROUP<00>                                            |     |

| 43 260.645199                             | 10.1.1.1                   | 10.255.255.255        | NBNS Registration NB TANGLES<00>                                              |     |

| 44 262.974875                             | 10.1.1.1                   | 224.0.0.2             | ICMP Router solicitation                                                      |     |

| 45 266.223654<br>46 266.274359            |                            | Broadcast<br>10.1.1.2 | ARP Who has 10.1.1.2? Tell 10.1.1.1<br>TCP 1030 > http [SYN] Seg=0 Ack=0 Win= |     |

| 40 200.274359                             | 10.1.1.1                   | 10.1.1.2              | TCP 1030 > http [SYN] Seq=0 Ack=0 Win=                                        | 1   |

| <                                         |                            |                       |                                                                               |     |

|                                           | P: 2266 D: 2266 M: 0       |                       |                                                                               |     |

Figure 4.7: Plethora of packets received on establishment of Link.

It is expected that the RAM utilisation can be easily reduced to around 1 kB (150 B for transmit and temporary buffers, 500 B for receive buffer and 200 B for the stack) which would be better suited to smaller devices.

#### 4.9 Code Optimisation

Currently the prototype systems occupies a code envelope of 8 kB. This is discussed in more detail, including further work, in Chapter 6.

### 4.10 Chapter Summary

This chapter has discussed the challenges encountered during this research project and some of the difficulties working with an embedded system utilising the Internet Protocols. It was interesting to discover that the Network (IP) and Transport layers (TCP) were closely bound and how it presented implementation issues with the Pseudo Header checksum calculation.

### Chapter 5

## **Testing and Security**

#### 5.1 Chapter Introduction

This chapter introduces the system testing activities performed so far. The security measures implemented and security considerations which are important to embedded devices are also discussed. As the project has been primarily been focused on the software implementation some hardware testing is discussed.

#### 5.2 Testing So Far

The testing of this system has evolved through-out the project in line with the services which were required for each project steps. The project began with the initial set-up and testing of the basic EIA232 communication, the PPP link, then the IP and finally the TCP layers to provide a working prototype.

The first step was the establishment of the basic EIA232 communication. This was a simple task as 'C' provided functions to send and receive bytes through the USART. The AVRCodeVision IDE code wizard was used to set-up the communication parameters of the port and a simple program was written to echo the characters send from a PC.

The first challenge of the project was the implementation of the HDLC packet which was fundamental to the operation of the TCP/IP stack as it provides the data link between systems. The formulation of the HDLC was relatively easy however the calculation of the Checksum provided some challenges. The packet analyser 'Ethereal' was found to be invaluable in the debugging process to provide feedback that the correct HDLC packet was formed and sent with the correct checksum. Various packets were formulated and sent to and from the embedded system to test the operation. This testing, with the assistance of 'Ethereal', proved that the software algorithms were functional correctly including the reception and transmission of the correct escape sequences (7E, 7D, and anything below 20 hex).

The process of testing with ethereal was extended to testing of the IP and TCP protocols. It is interesting to note that the way in which the TCP/IP suite operates. If you do not have the correct structure in your packets it just ignores them and 'Ethereal' again was used to debug malformed packets. For interest Figure 5.1 reveals a screen shot of 'Ethereal' capturing a malformed TCP checksum.

| © 13                 | JulyDump                                                                                                                                              | - Ethereal                                                                                                                | 1                                                                                   |                                             |                                     |                                             |                        |                          |               |       |                |                 |    |         |       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------|---------------------------------------------|------------------------|--------------------------|---------------|-------|----------------|-----------------|----|---------|-------|

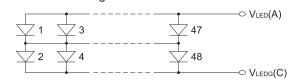

| Eile                 | <u>E</u> dit <u>V</u> iew                                                                                                                             | <u>G</u> o <u>C</u> aptu                                                                                                  | ure <u>A</u> naly                                                                   | ze <u>S</u> tati                            | stics <u>H</u>                      | lelp                                        |                        |                          |               |       |                |                 |    |         |       |