# Low-Cost Control System for Pop-Up Escape Room

A Thesis submitted by

Mr Kieran Bryce Davey

For the award of

Bachelor of Engineering (Honours)(Computer Systems)

2024

#### University of Southern Queensland

# School of Engineering ENP4111 Research Project

#### Limitations of Use

The Council of the University of Southern Queensland, its School of Engineering, and the staff of the University of Southern Queensland, do not accept any responsibility for the truth, accuracy or completeness of material contained within or associated with this dissertation.

Persons using all or any part of this material do so at their own risk, and not at the risk of the Council of the University of Southern Queensland, its School of Engineering or the staff of the University of Southern Queensland.

This dissertation reports an educational exercise and has no purpose or validity beyond this exercise. The sole purpose of the course pair entitled "Research Project" is to contribute to the overall education within the student's chosen degree program. This document, the associated hardware, software, drawings, and other material set out in the associated appendices should not be used for any other purpose: if they are so used, it is entirely at the risk of the user.

# University of Southern Queensland Faculty of Health, Engineering and Sciences ENG4111/ENG4112 Research Project

#### **Certification of Dissertation**

I certify that the ideas, designs and experimental work, results, analyses and conclusions set out in this dissertation are entirely my own effort, except where otherwise indicated and acknowledged.

I further certify that the work is original and has not been previously submitted for assessment in any other course or institution, except where specifically stated.

K. Davey

#### **ABSTRACT**

**Keywords:** Escape Room, Configurable Embedded Control System, Master-Slave Architecture, JSON.

The escape room industry provides an effective medium for recreational and educational activities. Significant accessibility challenges exist in automating the narratives of escape room experiences for non-technical designers due to resourcing costs. This project addresses these challenges by designing, developing and evaluating the suitability of a low-cost control system for escape room usage. The research aims to implement flexible progression logic and wireless communication through configuration files to reduce the technical barriers to industry adoption.

The control system was developed as a scalable master-slave architecture using JSON files for system configuration and communication. Bluetooth BLE was employed to achieve low-cost, multi-room wireless communication, while nested JSON structure facilitates the representation of hybrid progression logic paths. The control system components underwent unit, integration and system testing to demonstrate the ability to meet industry-specific objectives and outcomes in controlled conditions.

The study contributes a solution to the escape room industry by addressing the technical barriers introducing significant resourcing costs. Integrating nested JSON configuration files into the master-slave control architecture provides an abstract interface for developing immersive escape room narratives. The system was validated within controlled conditions. Therefore, future work should address real-world operational tests and the development of additional tools, such as graphical web interfaces for configuration file compilation and real-time monitoring.

The work presented within the study provides a strong foundation for a low-cost control system for pop-up escape rooms. This makes complex escape room narratives more accessible for recreational and educational applications.

#### **ACKNOWLEDGEMENTS**

I want to thank my supervisor, Ms Catherine Hills. I acknowledge her continual support and wisdom throughout the year. She consistently guided the project's progress despite being very busy with her role at the University. I am thankful for her time, patience, and kindness, demonstrated by going above and beyond what was required. I am grateful towards the University of Southern Queensland for providing the facilities and content to learn the information necessary to complete this project.

I am deeply grateful for the support of Brenden Davey, Vicki Davey, Elijsha Krushka, Issac Davey, Samuel Davey, Samuel Krushka and Tram Le Kim. This is my family, and they have been load bearers when I struggled throughout the project. They consistently encouraged me to push through the year-long research project and to strive for a high standard of excellence. I am also thankful to my close friends Luke Whittingham, Isaac Humber, and Jacob Moffatt. Your friendship has provided support and encouragement.

I will never forget the sacrifice of Mrs Wendy Horne and Mr Allen Westman. As I struggled with dyslexia growing up, both mentors believed and turned my educational weaknesses into strengths.

I acknowledge the mighty hand of my saviour, Yeshua ha'Mashiah. I would not be here without my Elohim, who has been my rock, light, and sure foundation throughout this project.

I dedicate this project to all those listed above. Thank you for your belief and commitment, as this project wouldn't exist without you.

# **TABLE OF CONTENTS**

| ABSTRACT     |                                                         | i    |

|--------------|---------------------------------------------------------|------|

| ACKNOWLED    | GEMENTS                                                 | ii   |

| LIST OF TABL | _ES                                                     | viii |

| LIST OF FIGU | JRES                                                    | x    |

| ABBREVIATIO  | DNS                                                     | xi   |

| CHAPTER 1:   | INTRODUCTION                                            | 1    |

| 1.1.         | Introduction and Background                             | 1    |

| 1.2.         | Objectives and Aims                                     | 2    |

| CHAPTER 2: I | LITERATURE REVIEW                                       | 4    |

| 2.1.         | Overview of the Escape Room Industry and Design         | 4    |

| 2.1.1.       | Escape Room Industry                                    | 4    |

| 2.1.2.       | Technologies within the Escape Room Industry            | 6    |

| 2.1.3.       | Escape Room Design and Implementation                   | 7    |

| 2.2.         | Control System Architectures for Escape Rooms           | 8    |

| 2.2.1.       | Overview of Control System Architectures                | 8    |

| 2.2.2.       | Control System Requirements                             | 9    |

| 2.3.         | Communication Strategies for Escape Room Control System | 10   |

| 2.3.1.       | Overview of Wireless Communication Methods              | 10   |

| 2.3.2.       | Bluetooth Wireless Communication                        | 11   |

| 2.3.3.       | LoRa Wireless Communication                             | 12   |

| 2.3.4.       | Wi-SUN Wireless Communication                           | 13   |

| 2.4.         | Configuration and Logic Definition Files                | 13   |

| 2.4.1.       | Overview of Configuration and Logic Definition Files    | 13   |

| 2.4.2.       | Configuration and Control Logic File Format Types       | 16   |

| 2.4.3.       | Abstract Data Types and Structures for Control Logic    | 18   |

| 2.4.4.       | Control System Logic Programming                        | 19   |

| 2.5.         | Literature Review Summary                               | 21   |

| CHAPTER 3: I | METHODOLOGY                                             | 25   |

| 3.1.1.       | Research Design                                         | 25   |

| 3.1.2.       | List of Materials                                       | 27   |

| 3.1.3.       | Risk Assessment                                         | 27   |

| 3.1.         | Development Process                                     | 27   |

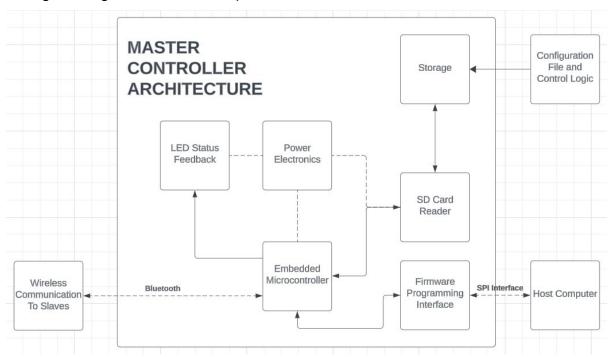

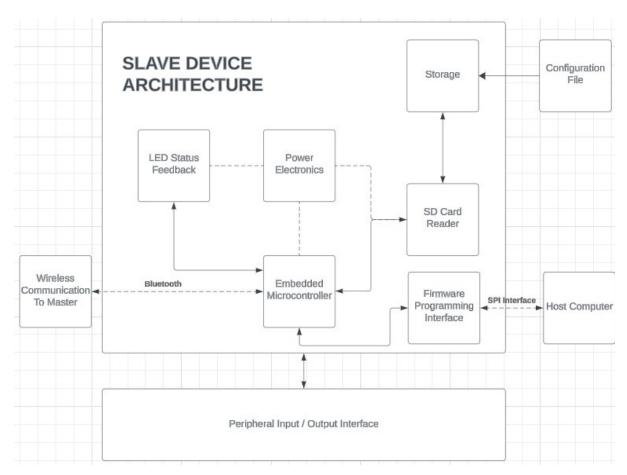

|      | 3.1.1.         | Embedded Architecture of Master Controller and Slave                 |      |

|------|----------------|----------------------------------------------------------------------|------|

| Со   | ntroller.      | 28                                                                   |      |

|      | 3.1.2.         | Embedded JSON Serialiser                                             | . 30 |

|      | 3.1.3.         | Bluetooth BLE Connection Interface                                   | . 31 |

|      | 3.1.4.         | Master Controller Configuration                                      | . 32 |

|      | 3.1.5.         | Slave Controller Configuration                                       | . 33 |

|      | 3.1.6.         | Master Controller's Control Logic Engine                             | . 34 |

|      | 3.1.7.         | Slave Controller's Control Logic Engine                              | . 35 |

|      | 3.1.8.         | Command Message Communication                                        | . 37 |

|      | 3.1.9.         | Master Controller's and Slave Controller's Communication             |      |

| En   | gine           | 38                                                                   |      |

|      | 3.1.10.        | Master Controller Initialisation and Slave Controller Initialisation | on.  |

|      | 3.1.11.        | Master Controller Configuration and Control Logic Engine             |      |

| Inte | egration.      | 39                                                                   |      |

|      | 3.1.12.        | Master Controller's Control Logic Action Dispatcher and              |      |

| Со   | mmunication A  | ction Dispatch Integration                                           | . 39 |

|      | 3.1.13.        | Slave Controller's Control Logic Action Dispatcher and               |      |

| Со   | mmunication A  | ction Dispatch Integration                                           | . 40 |

|      | 3.1.14.        | Operational Escape Room Purpose Testing                              | . 40 |

|      | 3.1.15.        | Operational Escape Room User Purpose Testing                         | . 41 |

|      | 3.1.16.        | Operational Communication Coverage Performance Testing               | . 42 |

|      | 3.1.17.        | Operational Communication Latency Performance Testing                | . 42 |

|      | 3.1.18.        | Concurrent Slave Controller Communication to Master Control          | ller |

| Pe   | rformance Test | ing                                                                  | . 43 |

|      | 3.1.19.        | Concurrent Control Logic Evaluation Performance Testing              | . 43 |

|      | 3.2. T         | esting Regime                                                        | . 44 |

|      | 3.2.1.         | Unit Testing                                                         | . 44 |

|      | 3.2.2.         | Integration Testing                                                  | . 79 |

|      | 3.2.3.         | System Testing                                                       | . 84 |

|      | 3.2.4.         | Performance Testing                                                  | . 87 |

| СН   | APTER 4: RES   | SULTS                                                                | . 94 |

|      | 4.1. T         | esting Process                                                       | . 94 |

|      | 4.1. E         | mbedded Architecture of Master Controller and Slave Controller       | r 94 |

| 4.2.          | Embedded JSON Serialiser                                             | 100     |

|---------------|----------------------------------------------------------------------|---------|

| 4.3.          | Bluetooth BLE Connection Interface                                   | 107     |

| 4.4.          | Master Controller Configuration                                      | 109     |

| 4.5.          | Slave Controller Configuration                                       | 110     |

| 4.6.          | Master Controller's Control Logic Engine                             | 111     |

| 4.7.          | Slave Controller's Control Logic Engine                              | 120     |

| 4.8.          | Communication Engine                                                 | 123     |

| 4.9.          | Master Controller and Slave Controller Communication Engin           | e 127   |

| 4.10.         | Master Controller Initialisation and Slave Controller Initialisation | on. 128 |

| 4.11.         | Master Controller's Configuration Engine and Control Logic E         | ngine   |

| Integration   | 129                                                                  |         |

| 4.12.         | Master Controller's Control Logic Engine and Communication           | 1       |

| Engine Integr | ation                                                                | 130     |

| 4.13.         | Slave Controller's Control Logic Engine and Communication            | Engine  |

| Integration   | 131                                                                  |         |

| 4.14.         | Operational Escape Room Purpose Testing                              | 132     |

| CHAPTER 5:    | DISCUSSION                                                           | 136     |

| 5.1.          | Introduction to Discussion                                           | 136     |

| 5.1.1.        | Research Objectives and Outcomes                                     | 136     |

| 5.1.2.        | Overview of Key Findings                                             | 137     |

| 5.2.          | Interpretation of Results                                            | 138     |

| 5.3.          | Implications of Findings                                             | 139     |

| 5.3.1.        | Implications for educational and recreational accessibility.         | 139     |

| 5.3.2.        | Implications for control system scale and flexibility in esca        | pe      |

| rooms.        | 139                                                                  |         |

| 5.4.          | Limitations of Study                                                 | 140     |

| 5.4.1.        | Overview of Limitations                                              | 140     |

| 5.4.2.        | Industry Specific Limitations                                        | 140     |

| 5.4.3.        | Limitations of Test Regime                                           | 141     |

| 5.4.4.        | Limitations of Design Decisions                                      | 141     |

| 5.4.5.        | Limitations of Constrained Scope                                     | 142     |

| 5.5.          | Suggestions for Future Research                                      | 142     |

| CONCLUSIO     | N                                                                    | 143     |

| REFERENCE     | S                                                                    | 144     |

| ΑP  | PENDICES        |                                                                     | .148  |

|-----|-----------------|---------------------------------------------------------------------|-------|

|     | 6.1. A          | Appendix A: Risk Assessment                                         | . 148 |

|     | 6.2. A          | Appendix B: Budget and List of Materials                            | . 149 |

|     | 6.3. A          | Appendix C: Unit Tests                                              | . 150 |

|     | 6.3.1.          | UT01 - Embedded Architecture of Master Controller                   | . 150 |

|     | 6.3.2.          | UT02 - Embedded Architecture of Slave Controller                    | . 156 |

|     | 6.3.3.          | UT03 – Embedded JSON Serialiser                                     | 164   |

|     | 6.3.4.          | Bluetooth BLE Connection Interface                                  | 184   |

|     | 6.3.5.          | Master Controller Configuration                                     | . 185 |

|     | 6.3.6.          | Slave Controller Configuration                                      | . 185 |

|     | 6.3.7.          | UT11 - Master Controller's Control Logic Engine Parser              | . 185 |

|     | 6.3.8.          | UT12 - Master Controller's Control Logic Engine Interpreter         | . 186 |

|     | 6.3.9.          | UT13 - Master Controller's Control Logic Engine State Manaç         | ger   |

|     | 6.3.10.         | UT14 - Slave Controller's Control Logic Engine Action Dispat<br>187 | cher  |

|     | 6.3.11.         | Command Message Communication                                       | . 187 |

|     | 6.4. A          | Appendix D: Integration Testing                                     | . 188 |

|     | 6.4.1.          | Master Controller and Slave Controller Communication Engir          | ne    |

|     | 6.4.2.          | Master Controller Initialisation and Slave Controller Initialisati  | on    |

|     | 6.4.3.          | Master Controller's Configuration Engine and Control Logic          |       |

| Eng | gine Integratio | n 188                                                               |       |

|     | 6.4.4.          | Master Controller's Control Logic Engine and Communication          | 1     |

| Eng | gine Integratio | n 188                                                               |       |

|     | 6.4.5.          | Master Controller's Configuration Engine and Control Logic          |       |

| Eng | gine Integratio | n 189                                                               |       |

|     | 6.4.6.          | Slave Controller's Control Logic Engine and Communication           |       |

| Eng | gine Integratio | n 189                                                               |       |

|     | 6.5. A          | Appendix E: System Testing                                          | . 190 |

|     | 6.5.1.          | Operational Escape Room Purpose Testing                             | . 190 |

|     | 6.5.2.          | Operational Escape Room User Purpose Testing                        | . 190 |

|     | 66 A            | Appendix F: Performance Testing                                     | 191   |

| 6.6.1.           | Operational Communication Coverage Performance Testing.     | 191  |

|------------------|-------------------------------------------------------------|------|

| 6.6.2.           | Operational Communication Latency Performance Testing       | 191  |

| 6.6.3.           | Concurrent Slave Controller Communication to Master Control | ller |

| Performance Test | ing                                                         | 191  |

| 6.6.4.           | Concurrent Control Logic Evaluation Performance Testing     | 191  |

# **LIST OF TABLES**

| Table 1: Unit Test UT01         | 44-45 |

|---------------------------------|-------|

| Table 2: Unit Test UT02         | 45-46 |

| Table 3: Unit Test UT03         | 46-47 |

| Table 4: Unit Test UT04         | 47-49 |

| Table 5: Unit Test UT05         | 49-50 |

| Table 6: Unit Test UT07         | 50-52 |

| Table 7: Unit Test UT08         | 52-53 |

| Table 8: Unit Test UT10         | 53-55 |

| Table 9: Unit Test UT11         | 55-57 |

| Table 10: Unit Test UT12        | 57-59 |

| Table 11: Unit Test UT13        | 59-61 |

| Table 12: Unit Test UT14        | 61-63 |

| Table 13: Unit Test UT15        | 63-66 |

| Table 14: Unit Test UT16        | 66-68 |

| Table 15: Unit Test UT17        | 69-70 |

| Table 16: Unit Test UT18        | 71-73 |

| Table 17: Unit Test UT19        | 73-74 |

| Table 18: Unit Test UT20        | 74-75 |

| Table 19: Unit Test UT21        | 75-77 |

| Table 20: Unit Test UT23        | 77-78 |

| Table 21: Unit Test UT24        | 78-79 |

| Table 22: Integration Test IT03 | 79-80 |

| Table 23: Integration Test IT04 | 80-81 |

| Table 24: Integration Test IT05 | 81-82 |

| Table 25: Integration Test IT06 | 82-83 |

| Table 26: Integration Test IT07 | 83-84 |

| Table 27: System Test ST01      | 85-86 |

| Table 28: System Test ST02      | 86-87 |

| Table 29: Performance Test PT01 | 87-88 |

| Table 30: Performance Test PT02 | 89-90 |

| Table 31: Performance Test PT03 | 90-92 |

| Table 32: Performance Test PT04                                    | 92-93   |

|--------------------------------------------------------------------|---------|

| Table 33: Master controller ESP32-C6-DevKit-1 v1.2 pin assignment. | 94      |

| Table 34: Slave controller ESP32-C6-DevKit-1 v1.2 pin assignment   | 95      |

| Table 35: UT01 outcome matrix                                      | 97      |

| Table 36: UT03 Outcome Matrix                                      | 103     |

| Table 37: UT04 Outcome Matrix                                      | 107-108 |

| Table 38: UT05 outcome matrix                                      | 109     |

| Table 39: UT07 outcome matrix                                      | 110     |

| Table 40: UT08 outcome matrix                                      | 110     |

| Table 41: UT10 outcome matrix                                      | 111     |

| Table 42: UT11 test case outcomes                                  | 118     |

| Table 43: UT12 test case outcomes                                  | 119     |

| Table 44: UT13 outcome matrix                                      | 119     |

| Table 45: UT13 outcome matrix                                      | 120     |

| Table 46: UT15 outcome matrix                                      | 121     |

| Table 47: UT16 outcome matrix                                      | 121     |

| Table 48: UT18 outcome matrix                                      | 122     |

| Table 49: UT19 outcome matrix                                      | 122-123 |

| Table 50: UT19 outcome matrix                                      | 123-124 |

| Table 51: UT20 outcome matrix                                      | 124-125 |

| Table 52: UT21 outcome matrix                                      | 125-126 |

| Table 53: UT21.2 outcome matrix                                    | 126     |

| Table 54: UT23 outcome matrix                                      | 126     |

| Table 55: UT24 outcome matrix                                      | 127     |

| Table 56: IT03 outcome matrix                                      | 128     |

| Table 57: IT04 outcome matrix                                      | 128     |

| Table 58: IT05 outcome matrix                                      | 129     |

| Table 59: IT06 outcome matrix                                      | 130     |

| Table 60: IT07 outcome matrix                                      | 131-132 |

| Table 61: ST01 outcome matrix 133-135                              |         |

## **LIST OF FIGURES**

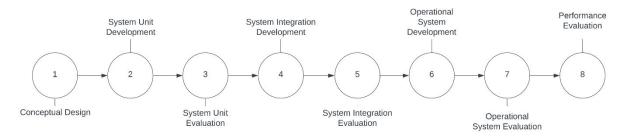

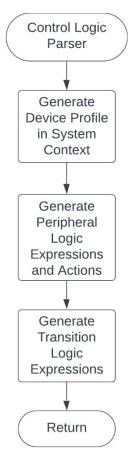

| Figure 1: Methodology Stage                                      | 25  |

|------------------------------------------------------------------|-----|

| Figure 2: Master Controller Architecture                         | 28  |

| Figure 3: Slave Device Architecture                              | 29  |

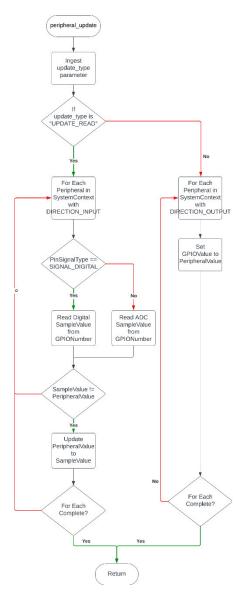

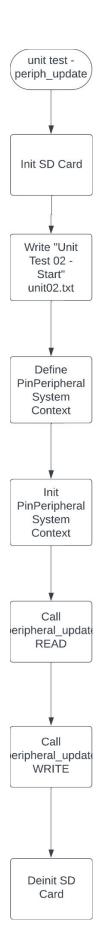

| Figure 4: peripheral_update process flow                         | 99  |

| Figure 5: json_schema_serialiser flow diagram                    | 101 |

| Figure 6: get_schema_content function prototype                  | 102 |

| Figure 7: SchemaPropertyMapping type definition                  | 102 |

| Figure 8: master control logic parser abstracted process diagram | 112 |

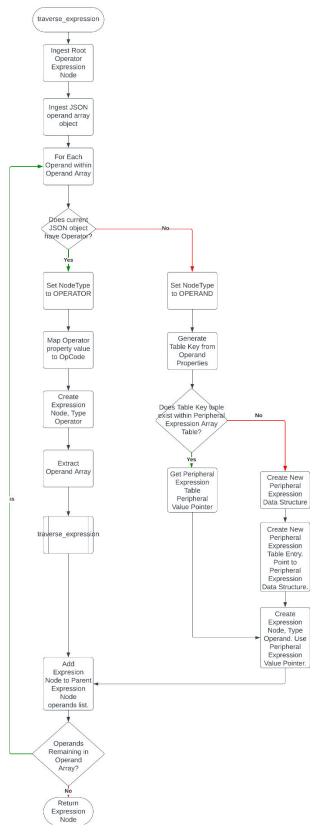

| Figure 9: traverse_expression process diagram                    | 113 |

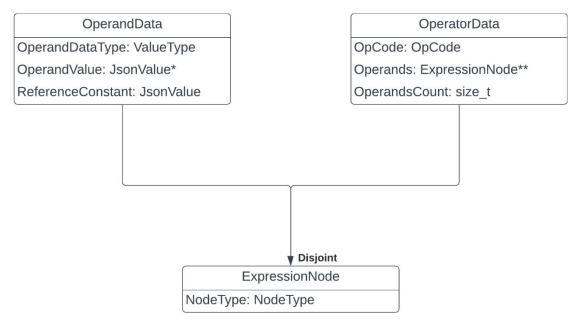

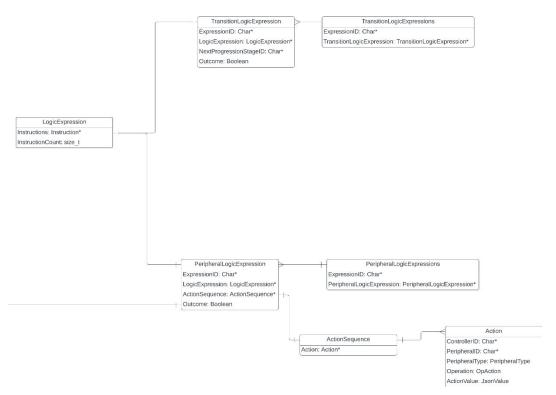

| Figure 10: ExpressionNode relationship to sub-types              | 114 |

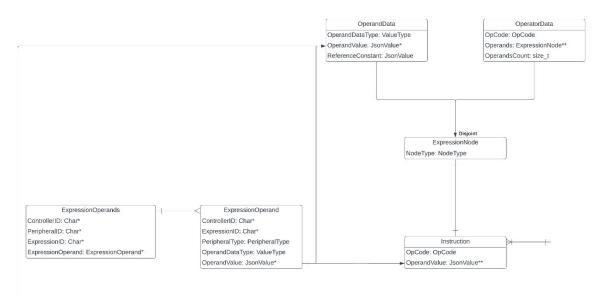

| Figure 11: expression structure relationships                    | 115 |

| Figure 12: Logic expression containing structures                | 116 |

| Figure 13: ST01 hybrid progression path                          | 133 |

#### **ABBREVIATIONS**

API: Application Peripheral Interface

FIFO: First In, First Out

FPGA: Field Programmable Gate Array

FSM: Finite State Machine

HMI: Human Machine Interface

JSON: JavaScript Object Notation

LED: Light Emitting Diode

MCU: Microcontroller Unit

RPN: Reverse Polish Notation

RSSI: Received Signal Strength Indicator

SD card: Secure Digital card

SPI: Serial Peripheral Interface

XML: Extensible Markup Language

#### **CHAPTER 1: INTRODUCTION**

#### 1.1. Introduction and Background

In recent years, escape rooms have emerged as a popular form of entertainment and problem-solving and have been recognised for their educational value (Li et al., 2018). Increasing research has recommended integrating escape room activities into formal, vocational, and adult education due to their interactive experience (Staneva et al., 2023). Escape rooms require teams of people to coordinate their collective competency and problem-solving skills to solve puzzles to escape their trapped rooms. The design and creation of exciting escape room designs require various technologies, ranging from mechanical puzzles to complex digital interfaces. Startup escape rooms have leveraged multiple technologies and complex control systems to create these compelling experiences (Inés Tejado et al. 2021). The cost of setting up and operating an escape room can vary widely; however, engineering sophisticated escape room logic, communication systems and control architecture for the puzzles is a significant investment (Tercanli et al., 2021). The system architecture must also be re-designed and engineered whenever the escape room experience or story is rewritten, requiring recurring investment to stay competitive. The review of such challenges demonstrates that engineering escape room puzzles and systems presents significant hurdles, particularly in integrating physical and digital elements. Research has proposed that virtual reality-based environments for escape rooms can mitigate the high material and integration costs (Darejeh, 2023). However, a solution for reducing the technical challenges and budget limitations for physical escape rooms remains unsolved.

Despite the growing popularity of escape rooms, there exists a noticeable gap in the market for a scalable, cost-effective control system that can accommodate the rapidly changing storylines of the escape room industry. Current escape room control systems require technical knowledge or have a high financial cost to produce an immersive narrative (Tercanli et al. 2021). This project proposes an abstracted, low-cost control system architecture tailored for non-technical escape room owners. The proposed system aims to implement a control system that runs on modular, wireless embedded systems, allowing game progression logic to be customised without programming knowledge. The game progression logic will be defined within a game file data structure and can be inserted into the reusable master-slave architecture via

an SD card. The system is designed to allow non-technical escape room designers to define game progression rules and logic. The research will investigate a scalable data structure supporting complex logic designs. The study will also examine the game progression file's ability to be compiled from highly abstracted user interfaces and interpreted by reusable embedded systems.

The project seeks to reduce the technical challenges and high financial costs sophisticated escape room owners encounter when designing new experiences. The project will enable the design of escape rooms to become highly abstracted from the hardware level, potentially creating a drag-and-drop graphical design experience.

#### 1.2. Objectives and Aims

#### **Specific Objectives:**

- The design of a low-cost master-slave control system architecture is suitable for escape room puzzles.

- Create a flexible escape room, progression logic file type and data structure that can be loaded onto the master and slave controllers via SD card.

- Implement master and slave interpreter for the game progression logic file data structure, ensuring accurate game progression and puzzle state management.

- Investigate coordination and scheduling schemes for master-slave communication, prioritising puzzle querying based on game progression.

- Analyse how different data file schemes impact system scalability and complexity.

- Evaluate and implement appropriate wireless communication methods,

protocols and technologies for the master and slave controllers.

- Investigate system usability limitations. Analysing system latency, data rate,

loss tolerance, wireless communication distance and response time.

- Evaluation of communication strategies such as suitability of polling versus interrupt-based methods for communication between master and slave devices.

If time permits,

- Develop a graphical web application to create the game progression logic.

- Develop a compiler that compiles the game progression logic into the master and slave game progression logic file.

#### **Expected Outcomes:**

- Low-cost, master controller embedded system with wireless communication,

SD card reader and game file interpreter.

- Low-cost, slave controller embedded system capable of wireless communication, SD card reader, game file interpreter and peripheral API for puzzle control.

- A robust communication method and data protocol tailored for master-slave interactions within the escape room environment.

- Definition and implementation of a universal game progression logic file data structure and file type that supports complex escape room game design.

- A game progression logic file interpreter on both master and slave devices, ensuring correct puzzle state management, game progression and data transfer.

- Implementation of an effective coordination scheme in the master controller to manage and query slave devices based on the current stage of the game progression.

- Understand the usage limitations and scalability of the modular control system.

If time permits,

- A web application for designing escape room game logic.

- Error handling and input validation of web application design tool user input.

- Implementation of a compiler to generate required game file format for master and slave controllers from graphical web application representation.

## **CHAPTER 2: LITERATURE REVIEW**

#### 2.1. Overview of the Escape Room Industry and Design

#### 2.1.1. Escape Room Industry

According to Gordon et al. (2019) findings, escape room activities positively influenced participants' perception of collaboration and teamwork compared to their perception of teamwork before the activities. Within the qualitative survey, 89% of students agreed that "I enjoy working in a team environment" after the escape room exercise as opposed to 79% before the exercise. 99% of the students strongly agreed that "I am an integral member of the team" after the exercise, as opposed to 94% before the escape room activities (Gordon et al., 2019). Escape room activities have also been shown to encourage problem-solving and cognitive function. The study conducted by Kinio et al. (2019) demonstrated that 75% of participants experienced a greater ability to retain the information from the interactive learning experience provided by the escape room. 92% of the students stated that the interactive learning format was appropriate for testing their knowledge retention (Kinio et al., 2019). The escape room activities undertaken by the students in both these studies suggest that escape rooms encourage not only effective cognitive function but also interactive social behaviour. Escape rooms are an effective medium for positively influencing the participants' perception of teamwork while solving problems.

The role of escape rooms as an educational tool has been utilised to promote engagement within low-motivation course content. The gamification of such educational material has increased student motivation and promoted transfer learning across theoretical and practical skills (Sánchez-Martín et al., 2020). Sánchez-Martín et al. (2020) conveyed that escape rooms can allow multiple methods for collecting data related to student learning. Escape rooms enable the students to be assessed through direct observation, questionnaires, and discussion groups. The engagement within these sessions increased due to the participants' personal experiences with the activities. Escape rooms have significantly impacted the education industry, facilitating greater student engagement and promoting critical thinking towards the learning activity. Cain (2019) derived that 91% of classroom students were more engaged in critical thinking due to the problem-solving associated with escape room activities.

89% of the classroom students also indicated that they enjoyed the escape room activity more than traditional education methods (Cain, 2019).

The escape room industry is becoming more competitive, and new escape room business trends have been consistently growing since 2014 (Spira, 2023). Spira (2023) indicates that one of the biggest challenges facing the escape room industry is the operating costs associated with building and testing new game narratives. This is magnified by the prolonged time it takes to develop new experiences and ensure that quality experience is produced. Another article by Lakomkina (2023) confirms this challenge by stating that escape room businesses' most significant challenge is the high initial investment required for equipment and software. Lakomkina also states that maintenance costs are high due to updating the escape room design and puzzles (Lakomkina, 2023).

Educational escape rooms also face a similar challenge of funding educational experiences when developing immersive experiences (Chang, 2019). These articles indicate that as the industry becomes increasingly competitive, there's a greater need to create new compelling experiences to keep consumer interest. The most significant hurdles in meeting this consumer expectation are the high initial cost and prolonged time needed to develop the technology and software integration. Tercanli et al. (2021) conducted an extensive study on the practical implementation of escape rooms in education. The research found that educator's technical and creative knowledge significantly inhibited the adoption of escape rooms in education.

Along with the technical hurdle in creating immersive educational experiences, the time and financial resources required to develop educational escape rooms are a significant challenge in integrating technologies into education. This highlights two common challenges, the first being the monetary and time cost of creating the technological integration of immersive escape room experiences. The second challenge is the technical knowledge required to develop and connect multiple technologies.

#### 2.1.2. Technologies within the Escape Room Industry

As the escape room industry is an emerging field of education and entertainment, there's limited literature categorising it into distinctive formats. However, multiple technology platforms have been researched to determine the ease of integration and implementation.

Kiruthika et al. (2022) explored the implementation of virtual reality to mitigate the resourcing costs associated with physical escape room props. Virtual reality escape room experiences enabled participants to interact with virtual objects and augmented audio-visual experiences. The user would then interact with the escape room through virtual user interface actions. The virtual environment allows the participants to experience interactions that would typically be difficult or unrealistic to implement within physical escape rooms, such as teleportation. The escape room environment was developed using 3D modelling and game development software. VR simulation headsets are then utilised to place the participant within the escape room environment, with the interactions being controlled through VR controllers (Kiruthika et al., 2022).

A standard format for escape room implementation is physical escape rooms. The participants must solve a combination of physical puzzles to progress into the next room. The development of the escape room puzzles requires a minimum competency in electronic design, with the programming complexity depending on the progression logic of the narrative (Ross, 2019). Ross (2019) explored a low-cost escape room puzzle design that required the escape room designer to acquire the electronic components, assemble the electronic components, and then configure the Arduino microcontroller by modifying and uploading code. The puzzles were implemented using Arduino Nano, LCD, number pad, speaker, and batteries. This resulted in an interactive puzzle that gave feedback to the user through the LCD screen resulting from user keypad input. There are eight challenges when designing a physical escape room, these being balancing the difficulty of the puzzles for the user, engineering competency in designing puzzle logic, creating room elements that don't break easily, integrating new puzzles into the existing narrative, getting the timing right between puzzles, developing a reconfigurable narrative and playtesting the escape room when developing (Ross, 2019). These challenges highlight the difficulty and technical knowledge required to design and develop physical puzzles. It was determined that advanced electronic and programming understanding would be essential for amending the system configuration. Ross (2019) found a gap in the system's ability to integrate with other puzzles and suggests integrating the puzzles with WIFI to configure and manage multiple puzzles simultaneously.

#### 2.1.3. Escape Room Design and Implementation

The design of an escape room should contribute towards motivating an engaging learning experience. This motivation is achieved by containing the participants within a locked room and requiring them to solve puzzles to escape. Escape rooms are often designed as fictional locations, facilitating an engaging learning experience. The complexity of automated fictional scenarios complicates the design of escape room stories. The complexity is introduced as the escape room game designer must consider an enjoyable, immersive experience without detracting from the educational lessons (Elmet Project, 2021). According to Tercanli et al. (2021), the narrative progression of escape rooms can be open, sequential, or path-based. An open escape room design allows the participant to solve the puzzles in any order to escape. The participants interacting with an open progression path narrative must complete the puzzles within the narrative successfully. However, the order of completion does not impact the successful escape of the room. Sequential escape room progression requires solving the puzzles in a particular sequential order. One puzzle completion would lead the participant to the next, allowing for successful completion once all puzzles are successfully passed in order. The hybrid path-based progression logic combines both open and sequential progression. The progression logic of such an escape room would depend on the outcome of the previous and current stages of the escape room (Tercanli et al., 2021). Hybrid path-based progression logic allows the narrative to branch into different paths depending on the outcome of puzzle interactions.

When designing escape rooms, a balance between entertainment value, progression logic complexity, and educational value is needed. When developing the escape room experience, balancing these necessary components is complicated for non-technical designers. The escape room designer must determine the educational competency

objectives, construct an engaging narrative, and then program the narrative's progression path into the control system's software and hardware design.

Ross & Bennett (2022) identified a diverse range of physical escape room puzzles that can exist in an escape room environment. Four escape rooms were designed, each with three puzzles. The diversity and strategic placement of the puzzles within each escape room were designed to suit different player skillsets. This promotes team collaboration and ensures each player within the team contributes. The first escape room was based on digital electronics competency. The three puzzles included C decoding, waveform decoding, and 7-segment display understanding. The second escape room was based on electronic hardware competency and included a measuring voltage, continuity testing, and LED lighting puzzle. The third escape room targeted STEM activities for high school engagement around STEM disciplines. The third escape room included puzzles on hydraulics, rotational equilibrium, and Caesar cipher. The fourth escape room was designed for testing international tertiary students. The three puzzles in this escape room tested Australian slang, Australian Geography and Australian Inventions (Ross & Bennett, 2022). The escape rooms designed by Ross & Bennett (2022) demonstrated that puzzles can be designed to support a variety of educational domains. However, the designer needs to be competent in electronic and programming disciplines to implement the puzzles. Escape room control systems must also be extensively tested to ensure the solution is possible without committing to developing the progression logic (Ross & Bennett, 2022).

#### 2.2. Control System Architectures for Escape Rooms

#### 2.2.1. Overview of Control System Architectures

Designing complex control systems is a technical and challenging process, even for competent escape room designers. The control system's design involves selecting controller hardware, interfacing the controller to the peripherals, and programming the control algorithms specific to the hardware implementation (Shaik, 2011). Shaik (2011) explored the implementation of a control system that utilised a 32-bit RISC microcontroller that offered compatibility with control system peripherals for real-time data acquisition. The study found that the microcontrollers' ability to utilize standard communication protocols allowed for network control and data acquisition from remote

locations. This emphasises the embedded system's ability to be scalable and flexible to expanding control systems and can be reprogrammed to meet various application requirements (Shaik, 2011). Peng et al. (2008) also investigated the approach to developing low-cost control systems by developing embedded controllers. The study found embedded control system architectures support advanced control logic through high computational capacity and open-source software packages. The microcontrollers' ability to communicate directly with sensors and actuators allows for a simplified development approach yet can also be scaled beyond the microcontroller's pinout through network capabilities (Peng et al., 2008).

Hanou et al. (2020) implemented a control system and interface for monitoring and configuring an escape room using the client-server architecture. The control system comprises a back-end server, a front-end user interface, and client computers. The back-end server was implemented using a Raspberry Pi, which managed the message broker, serving web interface and client device management. The back-end server serves the front-end and allows the escape room employee to monitor the state of the escape room. The client devices are puzzles that all have a unique IP address. The IP address allows client-server communication, which passes escape room state updates (Hanou et al., 2020). The control system implemented by Hanou et al. (2020) successfully passed field testing with suitable performance metrics. The control system requires all client devices and the server to have a unique IP address over the local area network and can connect to the network over WIFI.

#### 2.2.2. Control System Requirements

The design and selection of a control system architecture needs to consider the functional requirements and real-time characteristics of the control process. Therefore, control systems for the escape room industry need to scale and meet the operational requirements of escape room design.

Ross and Bennett (2022) demonstrated that an educational escape room narrative can have multiple puzzles included within its storyline. This outlines a one-to-many relationship between the controller and the puzzles it will need to manage. Therefore, a requirement of the control system architecture is that its performance does not degrade as the number of puzzles being managed scales. Different puzzles within the

same escape room narrative can also require different datatypes to be processed by the controller to trigger completion stages (Ross & Bennett, 2022). This highlights the requirement for the controller to be able to process multiple data types within the same escape room narrative.

Ross (2019) demonstrated that each puzzle within an escape room narrative can have multiple sensors and actuators, which need real-time processing in response to user interaction. From this another control system requirement is that the controller can process many peripheral state values for each puzzle. As the state of the puzzle peripherals is updated by user interaction, another requirement is that data can be processed in real time by interrupt (Ross, 2019). Tercanli et al. (2021) outlined that the escape room narrative's progression logic can be sequential and open. This results in path-based combinational logic, requiring the control system to process multiple puzzle data packets concurrently (Tercanli et al., 2021).

#### 2.3. Communication Strategies for Escape Room Control System

Understanding available wireless communication technologies and their typical characteristics is important for selecting a suitable option to achieve the control system's outcomes and objectives. The wireless communication methods assessed are Bluetooth, LoRa, and WiSUN. This contributes to achieving the objective of evaluating and implementing appropriate wireless communication methods, protocols, and technologies for the master and slave controller.

#### 2.3.1. Overview of Wireless Communication Methods

Goncalves et al. (2021) evaluated three low-power wireless communication technologies for SmartGrid networking applications. SmartGrid networks provide real-time monitoring, control signals, and data transfer for multiple power system devices. This has a similar relational multiplicity as the requirements defined for the escape room control system. Wireless communication technology within the escape room control system will need to allow for real-time data processing for multiple devices. Goncalves et al. (2021) investigated the performance characteristics of Bluetooth, LoRa and Wi-SUN wireless technologies to assess their suitability for SmartGrid networks. Coverage, data rate, power consumption, interoperability, physical layer

complexity, topology and worldwide acceptance were evaluated in the assessment (Goncalves et al., 2021).

#### 2.3.2. Bluetooth Wireless Communication

Park & Umirov (2012) presented the implementation use case of three different linktype profiles for Bluetooth communication in networked control systems. Serial Port Profile (SPP), Human Interface Device (HID) and Synchronous Connection-Oriented (SCO) were compared to assess their performance for communication between sensors, actuators, and controllers. SPP emulates a serial port over Bluetooth connection, allowing devices to communicate and simplify configuration and connection between devices. SPP was found to introduce non-linearity and unpredictable data packet ground, which can lead to latency issues (Park & Umirov, 2012). SCO is often utilised for real-time audio transmission using Bluetooth, as it allows for data streaming at low latency. The main limitation found with SCO is the limited support it provides in most Bluetooth modules. HID is commonly used for devices such as keyboards, mice and gaming controllers and is optimised for lowlatency communication. HID is supported by a wide range of devices and operating systems, making it suitable for networked control systems (Park & Umirov, 2012). The position control of a DC motor utilising these different link type profiles found that SPP is not recommended in use cases where low latency is required; however, it allows for simple configuration with the host controller interface (HCI). HID is preferred for lowlatency control systems; however, establishing connections with the HCI is more complex. This makes HCI more challenging in control systems that require direct control; however, it is the best choice where low latency and reliable connection are critical systems (Park & Umirov, 2012).

Goncalves et al. (2021) evaluated the performance characteristics of Bluetooth for SmartGrid systems with the following specifications. The coverage of Bluetooth was found to be limited to 100 meters, with the devices being assessed using a printed antenna of -6dBi gain. The coverage depended on how dense the obstacle conditions were within the operating environment. When operating within densely obstructed environments, the range was found to be 43m, while free space allowed for communication coverage of 242m (Goncalves et al., 2021). The data rate for Bluetooth is dependent on the version being implemented. Bluetooth 5.0 was found to allow data

rates of 1Mbps to 2Mbps. Bluetooth Low Energy provided data rates of 125kbps but could be increased to 500kbps when increasing the receiver sensitivity to -106.7 dBm. Bluetooth is suitable for battery-powered devices as it has low power consumption but depends on the chipset and other operating factors (Goncalves et al., 2021). Bluetooth allows for various network topologies, such as point-to-point connections and star configuration. This allows Bluetooth to be widely utilised globally, particularly in consumer electronics (Goncalves et al., 2021).

#### 2.3.3. LoRa Wireless Communication

Long Range (LoRa) communication is suitable for physically mobile applications and establishing a private network without a communication provider. It can transfer small data packets over a long-range network, connecting up to 1 million nodes (Anani et al., 2019). A LoRa network consists of a gateway, network server, application server and nodes. All nodes communicate through the gateway and commonly utilise the star topology. Angelov et al. (2023) investigated the suitability of a narrowband LoRa communication network for managing and monitoring an IoT lighting system. The control system implemented the LoRa system with sensors and actuators serving as nodes that communicate with a central LoRa gateway. The LoRa gateway then collected the data in a cloud-based server through a standard Wi-Fi network (Angelov et al., 2023). The LoRa network utilised three different node modules, with the mini module having a maximum range of 500 meters and the standard node modules having a maximum range of 900 meters. LoRa was a suitable selection for reliable control system communication while implementing optimised configurations, which significantly improved communication distance and reliability (Angelov et al., 2023).

Goncalves et al. (2021) evaluated the performance characteristics of LoRa for SmartGrid systems. The coverage of LoRa was able to establish a connection from 10km with an external antenna of 2dBi gain. In densely obstructed areas, the coverage was found to be 1.9km. The data rate for LoRa devices ranged from 0.3kbps to 50kbps. LoRa was determined to be suitable for battery-operated devices as it is designed for low power consumption. The devices utilising LoRa are standardised through Semtech Corp, which developed the technique and manufactured these modules. LoRa is designed to be implemented with the star topology with a centralised gateway managing the node devices (Goncalves et al., 2021).

#### 2.3.4. Wi-SUN Wireless Communication

The Wireless Smart Ubiquitous Network (Wi-SUN) is suitable for medium-range communication that requires low power consumption and high node density. Wi-SUN enables mesh topology, which can be complicated to configure but allows redundancy through network hopping if different nodes fail (Anani et al., 2019). Wi-SUN is suitable for metering infrastructure, distributed automation, and home area networks. The challenges related to Wi-SUN communication come from higher device costs and its tendency to be prone to interference (Anani et al., 2019). Kashiwagi et al. (2022) evaluated the suitability of Wi-SUN networks for the transmission performance of USB-type radio boards. The star and tree topology were tested, giving a packet transmission success rate over 95%. Due to multi-hop processing, the tree topology had a longer configuration time than the star topology (Kashiwagi et al., 2022). Both network topologies remained stable with no drop states for 12 hours of continuous operation. During this time, the power consumption was evaluated to enable the system to operate on two AA batteries for at least one year (Kashiwagi et al., 2022).

Goncalves et al. (2021) evaluated the performance characteristics of Wi-SUN for SmartGrid systems. Wi-SUN coverage established a connection from 7km with an external antenna of 2dBi gain. In densely obstructed areas, the coverage was found to be 1.3km. The data rate for Wi-SUN devices ranged from 50kbps to 300kbps. Wi-SUN was determined to be suitable for battery-operated devices as it is designed for low power consumption. Wi-SUN is designed to be implemented with the mesh topology, enabling it to scale well with the control system. The mesh topology does require more complicated communication management and can also have increased latency due to multiple network hops (Goncalves et al., 2021).

#### 2.4. Configuration and Logic Definition Files

#### 2.4.1. Overview of Configuration and Logic Definition Files

Configuration management allows for consistent operation of an embedded system and software across multiple product-level changes. Configuration management is a process and solution for system design that maintains the integrity of the system as it changes (TARAMAA et al., 1996). This is relevant to the implementation of an adaptable escape room control system as the same control system will need to be changed frequently to accommodate different escape room narratives. Suitable

configuration management will enable the embedded control system to evolve between narrative versions using a common configuration definition.

An industry-wide concern is that organisations have valuable software solutions that have consisted of different methodologies and technology stacks over time. Effective software configuration management allows organisations to adopt innovative solutions to remain competitive by defining consistent configuration schemes (TARAMAA et al., 1996). Mature configuration management solutions must implement change management controls and version management and are not dependent on specific hardware or software modules. Flexible software process design requires that configuration management and software process requirements are not codependent yet still retain the internal relationships between them. Configuration management solutions should facilitate the change management between existing software processes as they evolve (TARAMAA et al., 1996). TARA MAA et al. (1996) outline the process of defining configuration management into the stages of configuration identification, configuration control, configuration status accounting and configuration audit. The process of configuration identification involves defining the items of a product that will need configuration management. Configuration control defines the process and structures that support changes to the configuration items identified throughout the product life cycle. Configuration status accounting is the schemas that log and report the status of configuration items and their change requests. Configuration audit is the process that verifies the completion and correct implementation of the configuration items after changes (TARAMAA et al., 1996).

Configuration files allow developers to change the key-value pairs within an XML document to change the program settings, objects, and protected references without recompiling the system's source code (Kasbe, 2015). Effective implementation of configuration files enables flexibility in utilising the same source code across different system environments. Configuration files utilise XML key-value pairs to map system resources to reduce the cost of redeveloping source code for different control branches and initialisation cases. Kasbe (2015) focuses on the configuration files for .NET technology and outlines three different configuration file types. The application configuration file contains the pre-application configurations. The pre-application key-value pairs contain version control variables, enabling the system administrator to

select the versioning of source code modules, data storage paths and other initialisation values. The machine configuration file stores the global configuration values to be initialised across individual directories. The web configuration files store the configuration values for the web applications separate from the application source code configuration (Kasbe, 2015). Each of these three files is hierarchical, enabling configuration files further up the chain to overwrite the more granular values (Kasbe, 2015).

Gutjahr and Heumesser (2014) present a method for generating configuration files to maintain and administer computer systems. The configuration files generated define technical information and operational values to be monitored for a central server and its agents—the technical information defines device operational parameters such as allocated bandwidth or allowed communication protocols. The configured device can then send alerts and messages to the central server depending on the operational value thresholds defined (Gutjahr & Heumesser, 2014). Generating configuration files requires the central server to generate unique configuration file values for each agent. The generated configuration file must also generate the correct file structure and format depending on the agent architecture (Gutjahr & Heumesser, 2014). The method for generating configuration files by Gutjahr and Heumesser (2014) utilises a template XML file, XML data file and two XSTL style sheet sheets. The configuration file goes through three transforms to create the executable XML configuration file during generation. The first XSTL stylesheet transforms the XML data file where each query of the set of queries corresponds to an XPath expression (Gutjahr & Heumesser, 2014). The second XSTL, comprising the subset of parameter settings, takes the first transform and maps to the corresponding XPath expressions. The second XSTL maps the location of each parameter set to a location within the XML template (Gutjahr & Heumesser, 2014). The output from the second transformation is the XML configuration file, which is converted into its executable format.

Once the configuration files have been generated and validated, they must be distributed across the control system architecture. Lee et al. (2014) outlines a method that allows a master device to share its configuration files with its slave devices. This enables a control system to load a master configuration file to the master devices. Then, the master device distributes the corresponding configuration to each slave

device using the CANopen protocol (Lee et al., 2014). This enables the repair or update of specific slave devices within a control system from the master controller. The proposed implementation has the master device check the version of the configuration file against a directory on the host computer during system boot or startup. If the version stored on the master devices does not match the version on the host computer, the master device downloads the latest version from the host computer. The master devices then distribute the configuration object files to the slave devices in a feedback mode and validate that reconfiguration was successful. On successful reconfiguration, the master and slave devices may reboot depending on configuration settings (Lee et al., 2014).

#### 2.4.2. Configuration and Control Logic File Format Types

Configuration management implementation across distributed systems can involve configuration files using different file types. This introduces the challenge of maintaining or generating files for a control system as the system evolves. Elsner et al. (2011) propose a framework that validates consistent models across multiple configuration format types, fixes the errors according to rules and serialises back into the original format type. The proposed framework investigates the compatibility between Ecore DSMs, XText DSLs, XML schema XML, Java Property files and C header files (Elsner et al., 2011). Each config file has its own model. The round-trip mechanism then converts the configuration file to its defined model using its metamodel, which maps the configuration artefacts to the model. The universal model is then validated and fixed if necessary. Once validated and fixed according to the metamodel constraints, the round-trip mechanism converts the universal model back into the original configuration file format (Elsner et al., 2011).

Chrysalidis and Frank (2024) implemented a universal configuration format that managed unsynchronised and decentralised data for avionic systems. The configuration format leveraged the universal model approach to manage the configuration changes. The configuration management solution identified the configuration data into three different groups: devices, testing and network. The configuration file generation process was based on the eclipse modelling framework. Then the meta-model definitions were converted into the custom Universal

Configuration Format for Avionics (UCoF) configuration format (Chrysalidis & Frank, 2024). This highlights the possibility of generating custom configuration formats based on meta-model definitions for application-specific use cases.

An alternative file format for configuration files is the JavaScript Object Notation (JSON) file format. The JSON file format can represent both the configuration of control system devices and the format that structures data for communication between control system devices (Wehner et al., 2014). This enables a single file format for configuration management and message parsing throughout the control architecture. JSON is an international data processing standard that is human-readable, data interchangeable and lightweight file size format (Wehner et al., 2014). Wehner et al. (2014) experimented with a concept that utilised JSON to dynamically distribute the computational load of services across multiple FPGA nodes on an IoT network. The concept allowed users to stream video footage from one system service to another using the JSON file format. However, when the system receiving the streamed footage utilises all its resources, the image processing can be delegated to other nodes within the IoT network. This was achieved by utilising a standard JSON structure, allowing the streaming service to select the appropriate service by configuring key-value pairs. The payload of the image and its properties were also streamed within the same JSON data structure, enabling the image to be processed by the delegated node (Wehner et al., 2014). This demonstrates JSON's ability to configure control system devices while parsing the relevant data in a structured format.

Kasbe (2015) defines the implementation of configuration files as being in the Extensible Markup Language (XML) file format. XML stores the key-value pairs of object definitions through semantic tags (Kasbe, 2015). Despite being a standard format type for configuration files, XML has been proven to have greater processing overhead than JSON. This is due to the syntax structure of XML being more complex, requiring higher computation to parse. This can drain a significant proportion of the resources in embedded systems (Kasbe, 2015). This highlights the need for carefully selecting the configuration and data structure file type carefully depending on system resources and use case.

#### 2.4.3. Abstract Data Types and Structures for Control Logic

Organised and universal data structures allow for scalable and descriptive representation of a control systems state. The design of a control system requires the key system objectives to be identified and represented within a universal data structure. Mapping the key system objectives within a universal data structure allows it to be de-structured by different sub-systems (Vojir & Beran, 2015). Developing a hierarchical composite structure allows for a clean organisation of system parameters and commands. This allows programmers to easily modify and navigate the data structures (Vojir & Beran, 2015). Another advantage of universal data structures is that they support modular design principles. This allows the data structure to scale and adapt the structure for different applications while keeping consistent model schemas. This enables the designed data structure to be compatible across all devices in the control system despite different hardware and internal processes (Vojir & Beran, 2015).

Fuzzy logic represents control logic within control systems, which requires tolerating imprecise data and modelling non-linear functions. Fuzzy logic can manage partial truth values instead of standard discrete Boolean values (Chrysalidis & Frank, 2024). This is achieved by allowing a degree of truthfulness or falsehood around the control variables, which closely mimics human thinking and decision-making. Fuzzy logic implementations allow abstract or complex problem-solving to be modelled within an expert system model, allowing for flexible decision-making (Chrysalidis & Frank, 2024). Chrysalidis and Frank (2024) outline that fuzzy logic is common within embedded control systems and can be found within vehicle sub-systems, air conditioners, digital image processing and pattern recognition applications. The main limitation of fuzzy logic systems is the complexity of designing the membership functions and rule bases, which describe the control problem. Fuzzy logic implementations can also lack precision depending on how fine-tuned the rule description is. This requires precision tolerance to be understood in order to test the control system (Chrysalidis & Frank, 2024). Bashi (2024) investigated the application of fuzzy logic to manage traffic flow at intersections. The system adjusted the signal timing based on real-time traffic conditions. This aimed to reduce waiting time at the intersection and improve traffic flow in different traffic densities (Bashi, 2024). The fuzzy logic controller ingested real-time traffic data and utilised image processing to enhance the traffic condition parameters. The fuzzy logic controller then interpreted the traffic conditions based on the scale of each parameter to determine the wait time for each path (Bashi, 2024). Bashi (2024) found that the simulation reduced congestion and decreased vehicle wait time. The system also prioritised emergency vehicle paths, ensuring they experienced minimal delays (Bashi, 2024).

Finite State Machine (FSM) are real-time control structures that produce abstracted models from input alphabets. The input alphabet is converted into internal variables and states, producing an output alphabet that can be parsed as output values (Miroshnyk et al., 2018). FSMs are often represented as state diagrams, which visually describe the states, transitions between states and the actions of the FSM (Miroshnyk et al., 2018). Miroshnyk et al. (2019) developed a pattern for describing FSM in hardware description language for VHDL in FPGA applications. The resulting method utilised temporal state diagrams to represent a three-process control pattern. The temporal state diagram incorporates delays into the state diagram, enabling real-time control Miroshnyk et al., (2019). The results showed that the two-block FSM structure was successfully simulated and synthesised into the FPGA control system. This demonstrates FSM's ability to represent real-time logic control systems on embedded devices.

#### 2.4.4. Control System Logic Programming

Many real-time control logic programming languages have been established, each with its own strengths and limitations. Some of these control structure languages are finite state machines (FSM), design structure diagrams (DSD), function block diagrams, ladder logic and sequential function charts (Mallaband, 1991). Mallaband (1991) established criteria for selecting the programming technique for real-time control systems. The main factors that need to be considered are the characteristics of the controlled system, the application domain of the control system, the familiarity with user training and experience, the architecture model that defines the control system and the features that need to be described by the programming technique (Mallaband, 1991).

Ladder logic diagrams have been a long-standing standard for representing control logic in programmable logic controllers. It has been the preferred language and widely accepted due to its fundamental programming elements mimicking discrete logic primitives (Wareham, 1988). Wareham (1988) identifies that a limitation of ladder logic is that it does not easily represent multiple events occurring concurrently. Rather, ladder logic is formatted so that the program scans the rungs of the control process sequentially (Wareham, 1988). Control rungs should be organised into zones and incorporate jump statements and sub-routines to facilitate the simultaneous processing of independent operations. This can make the program lengthy and difficult to design, so it scales with added complexity (Wareham, 1988).

An alternative to ladder logic is sequential function charts. Sequential function charts are an international standard representing the control logic graphically using function blocks, steps, and conditional transitions (Wareham, 1988). Sequential function charts can represent command- and event-driven systems and handle concurrency in a single structure (Mallaband, 1991). Mallaband (1991) outlined the specification for representing real-time control systems with sequential function charts. Function blocks represent the actions executed when a step is active. A functional block can either be stored or not, impacting whether the state persists beyond the step's activity. The steps represent specific states within the control process. The steps organise the control logic into distinct phases associated with control commands. Finally, conditional transitions define the conditions in which the control process moves between steps. The conditional transitions control the process flow based on the conditions defined (Mallaband, 1991).

Ivanescu et al. (2007) present a method for process control in embedded systems using sequential function charts. The method successfully demonstrated the ability of microcontrollers to interpret and execute multiple SFCs with efficient control processes. The major limitation of running SFCs on microcontroller devices is the memory capacity of embedded systems and the implementation requiring a reduced number of input/output pins (Ivanescu et al., 2007). Ivanescu et al. (2007) implemented this with an infinite loop function, which is continuously called three functions: input acquisition, SFC executions, and output update. The microcontroller interpreted each SFC step as a C function and executed the defined actions based on

the transition conditions. Once the step definition was interpreted, the microcontroller would execute the associated actions as one-time or continuous. The transition conditions were evaluated within each step function execution to determine if the next step was in the state (Ivanescu et al., 2007). The implementation also managed parallelism and convergence by separating converging elements into separate SFC charts. The main loop process would update pointers to ensure they were executed in the next cycle (Ivanescu et al., 2007). This demonstrates the practical application of SFC diagrams in embedded systems and their ability to handle complex control processes.

#### 2.5. Literature Review Summary

The current literature review highlights the clear benefits of escape room experiences within the recreational and educational industries. The exercises promote team collaboration and social interaction through problem-solving (Gordon et al., 2019). The literature also demonstrates that escape room experiences enable an immersive learning experience and enhance transfer learning for low-motivation topics (Sánchez-Martín et al., 2020). With these benefits, the escape room industry continues to grow; however, it faces consistent resourcing challenges (Lakomkina, 2023). The resourcing challenges result from integrating the control technology with the quickly changing story narratives of the escape room design (Tercanli et al., 2021). This identifies a gap within the literature that needs to be resolved to allow non-technical escape room designers to develop escape room experiences at a low cost.

Multiple technologies have been researched to develop escape room narratives without the need for computer programming or electronic competency. Virtual reality escape rooms enable the users to interact within virtually immersive environments and allow the participants to interact with them through VR controllers and headsets (Kiruthika et al., 2022). Physical escape room experiences were shown to be able to test educational competency across a variety of educational domains but require the knowledge to configure and engineer the puzzles (Kiruthika et al., 2022). Ross (2019) outlines the need for the puzzles within the narrative to communicate with one another and integrate within a control system. This would enable the automatic progression throughout the escape room stages (Ross, 2019).

The control system architecture of an escape room would need to scale with a one-to-many relationship between the controller and its puzzles (Ross & Bennett, 2022). The puzzles within the control system would also require the controller to interpret different data types depending on user interaction with the puzzle. This highlights the need for the control architecture to process multiple datatypes within the same escape room narrative (Ross & Bennett, 2022). The control system would need to process a single puzzle's many sensor and actuator values. This would require that the control system be able to process multiple asynchronous puzzle interactions simultaneously. However, each puzzle interaction would also require processing many sensor and actuator values within each puzzle data structure (Ross, 2019). The control system logic representation would be required to represent path-based combinational logic (Tercanli et al., 2021). This control logic representation would need to scale with the many peripherals and puzzles that impact the system state. The path-based combinational logic presents the need for multiple data packets to be processed concurrently (Tercanli et al., 2021).

The performance characteristics of different wireless communication methods have been researched to achieve a pop-up escape room at a low cost. Bluetooth, LoRa, and Wi-SUN protocols have different performance characteristics and compatible topologies. Bluetooth was suitable for point-to-point and star topology communication use cases compatible with the master-slave architecture (Goncalves et al., 2021). Goncalves et al. (2021) state that Bluetooth can achieve a coverage of 43m in densely obstructed areas and provides data rates of 125kbps. There is a gap in understanding of the ideal implementation of wireless communication methods for low-cost escape room control systems. The selection of wireless communication methods will depend upon the performance characteristics and ease of automatic connection configuration.

Scalable configuration management would be required to implement a universal control system for differing escape room narratives. Well-defined configuration management would enable consistent control system operation independent of the hardware and process control logic (TARAMAA et al., 1996). Flexible implementation of control processes and hardware systems requires configuration management and systems to be not co-dependent. Rather, the relationship models between the system